A. Saba & N. Manna

Ë N G I N E E R I N G S E R I E S

Digital Principles and Logic Design

#### LICENSE, DISCLAIMER OF LIABILITY, AND LIMITED WARRANTY

The CD-ROM that accompanies this book may only be used on a single PC. This license does not permit its use on the Internet or on a network (of any kind). By purchasing or using this book/CD-ROM package(the "Work"), you agree that this license grants permission to use the products contained herein, but does not give you the right of ownership to any of the textual content in the book or ownership to any of the information or products contained on the CD-ROM. Use of third party software contained herein is limited to and subject to licensing terms for the respective products, and permission must be obtained from the publisher or the owner of the software in order to reproduce or network any portion of the textual material or software (in any media) that is contained in the Work.

INFINITY SCIENCE PRESS LLC ("ISP" or "the Publisher") and anyone involved in the creation, writing or production of the accompanying algorithms, code, or computer programs ("the software") or any of the third party software contained on the CD-ROM or any of the textual material in the book, cannot and do not warrant the performance or results that might be obtained by using the software or contents of the book. The authors, developers, and the publisher have used their best efforts to insure the accuracy and functionality of the textual material and programs contained in this package; we, however, make no warranty of any kind, express or implied, regarding the performance of these contents or programs. The Work is sold "as is" without warranty (except for defective materials used in manufacturing the disc or due to faulty workmanship);

The authors, developers, and the publisher of any third party software, and anyone involved in the composition, production, and manufacturing of this work will not be liable for damages of any kind arising out of the use of (or the inability to use) the algorithms, source code, computer programs, or textual material contained in this publication. This includes, but is not limited to, loss of revenue or profit, or other incidental, physical, or consequential damages arising out of the use of this Work.

The sole remedy in the event of a claim of any kind is expressly limited to replacement of the book and/or the CD-ROM, and only at the discretion of the Publisher.

The use of "implied warranty" and certain "exclusions" vary from state to state, and might not apply to the purchaser of this product.

Digital Principles and Logic Design

> A. SAHA N. MANNA

INFINITY SCIENCE PRESS LLC Hingham, Massachusetts New Delhi Reprint & Revision Copyright © 2007. INFINITY SCIENCE PRESS LLC. All rights reserved. Copyright © 2007. Laxmi Publications Pvt. Ltd.

This publication, portions of it, or any accompanying software may not be reproduced in any way, stored in a retrieval system of any type, or transmitted by any means or media, electronic or mechanical, including, but not limited to, photocopy, recording, Internet postings or scanning, without prior permission in writing from the publisher.

Publisher: David F. Pallai

INFINITY SCIENCE PRESS LLC 11 Leavitt Street Hingham, MA 02043 Tel. 877-266-5796 (toll free) Fax 781-740-1677 *info@infinitysciencepress.com www.infinitysciencepress.com*

This book is printed on acid-free paper.

A. Saha and N. Manna. *Digital Principles and Logic Design*. ISBN: 978-1-934015-03-2

The publisher recognizes and respects all marks used by companies, manufacturers, and developers as a means to distinguish their products. All brand names and product names mentioned in this book are trademarks or service marks of their respective companies. Any omission or misuse (of any kind) of service marks or trademarks, etc. is not an attempt to infringe on the property of others.

Library of Congress Cataloging-in-Publication Data

Saha, A. (Arjit)

Digital principles and logic design / A. Saha and N. Manna.

p. cm.

Includes bibliographical references and index.

ISBN 978-1-934015-03-2 (hardcover with cd-rom : alk. paper)

1. Electric circuits--Design and construction. 2. Digital electronics. 3. Logic design. I.

Manna, N. (Nilotpal) II. Title.

TK454.S3135 2007

621.319'2--dc22

#### 2007013970

$07\ 8\ 9\ 5\ 4\ 3\ 2\ 1$

Our titles are available for adoption, license or bulk purchase by institutions, corporations, etc. For additional information, please contact the Customer Service Dept. at 877-266-5796 (toll free in US).

Requests for replacement of a defective CD-ROM must be accompanied by the original disc, your mailing address, telephone number, date of purchase and purchase price. Please state the nature of the problem, and send the information to INFINITY SCIENCE PRESS, 11 Leavitt Street, Hingham, MA 02043.

The sole obligation of INFINITY SCIENCE PRESS to the purchaser is to replace the disc, based on defective materials or faulty workmanship, but not based on the operation or functionality of the product.

Dedication To our parents who have shown us the light of the world.

## **CONTENTS**

| Preface | face (                              |    |

|---------|-------------------------------------|----|

|         |                                     |    |

| 1. DA'  | TA AND NUMBER SYSTEMS               | 1  |

| 1.1     | Introduction                        | 1  |

| 1.2     | Number Systems                      | 2  |

| 1.3     | Conversion between Number Systems   | 2  |

| 1.4     | Complements                         | 10 |

| 1.5     | Binary Arithmetic                   | 13 |

| 1.6     | 1's And 2's Complement Arithmetic   | 17 |

| 1.7     | Signed Binary Numbers               | 19 |

| 1.8     | 7's And 8's Complement Arithmetic   | 21 |

| 1.9     | 9's And 10's Complement Arithmetic  | 23 |

| 1.10    | 15's And 16's Complement Arithmetic | 25 |

| 1.11    | BCD Addition                        | 27 |

| 1.12    | BCD Subtraction                     | 28 |

|         | Review Questions                    | 30 |

| 2. COI  | DES AND THEIR CONVERSIONS           | 31 |

| 2.1     | Introduction                        | 31 |

| 2.2     | Codes                               | 31 |

| 2.3     | Solved Problems                     | 44 |

|         | Review Questions                    | 49 |

| 3. BO   | DLEAN ALGEBRA AND LOGIC GATES       | 51 |

| 3.1     | Introduction                        | 51 |

| 3.2     | Basic Definitions                   | 51 |

| 3.3     | Definition of Boolean Algebra       | 52 |

| 3.4     | Two-valued Boolean Algebra          | 54 |

| 3.5    | Basic Properties And Theorems of Boolean Algebra | 55          |

|--------|--------------------------------------------------|-------------|

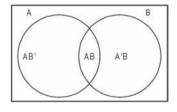

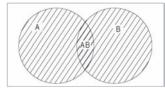

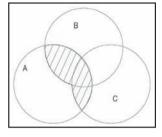

| 3.6    | Venn Diagram                                     | 57          |

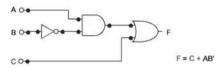

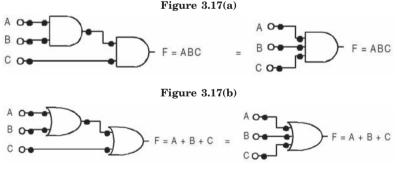

| 3.7    | Boolean Functions                                | 58          |

| 3.8    | Simplification of Boolean Expressions            | 59          |

| 3.9    | Canonical And Standard Forms                     | 60          |

| 3.10   | Other Logic Operators                            | 67          |

| 3.11   | Digital Logic Gates                              | 67          |

| 3.12   | Positive And Negative Logic                      | 83          |

| 3.13   | Concluding Remarks                               | 84          |

|        | Review Questions                                 | 85          |

| 4. SIM | IPLIFICATION AND MINIMIZATION OF BOOLEAN FU      | UNCTIONS 89 |

| 4.1    | Introduction                                     | 89          |

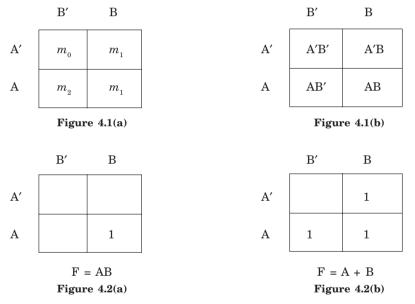

| 4.2    | Two-variable Karnaugh Maps                       | 89          |

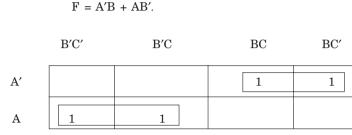

| 4.3    | Three-variable Karnaugh Maps                     | 90          |

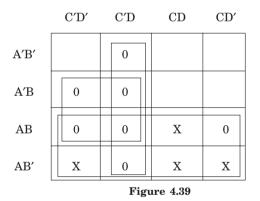

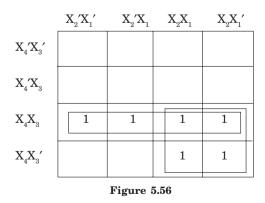

| 4.4    | Four-variable Karnaugh Maps                      | 93          |

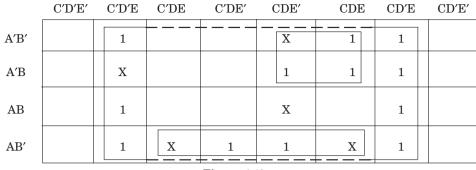

| 4.5    | Five-variable Karnaugh Maps                      | 99          |

| 4.6    | Six-variable Karnaugh Maps                       | 100         |

| 4.7    | Don't-care Combinations                          | 102         |

| 4.8    | The Tabulation Method                            | 103         |

| 4.9    | More Examples                                    | 106         |

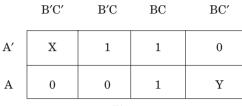

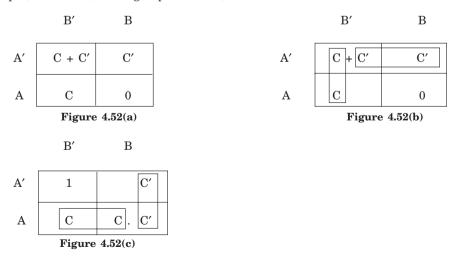

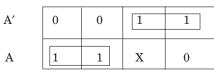

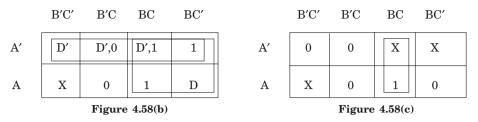

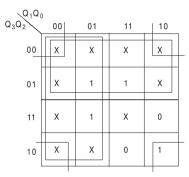

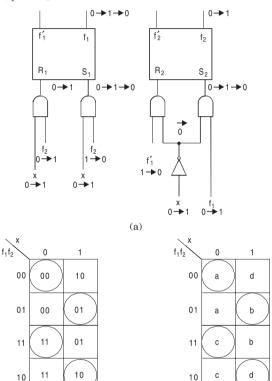

| 4.10   | Variable-entered Karnaugh Maps                   | 113         |

| 4.11   | Concluding Remarks                               | 123         |

|        | Review Questions                                 | 123         |

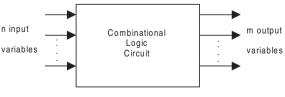

| 5. CO  | MBINATIONAL LOGIC CIRCUITS                       | 125         |

| 5.1    | Introduction                                     | 125         |

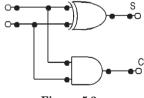

| 5.2    | Design Procedure                                 | 126         |

| 5.3    | Adders                                           | 126         |

| 5.4    | Subtractors                                      | 129         |

| 5.5    | Code Conversion                                  | 132         |

| 5.6    | Parity Generator And Checker                     | 141         |

| 5.7    | Some Examples of Combinational Logic Circuits    | 143         |

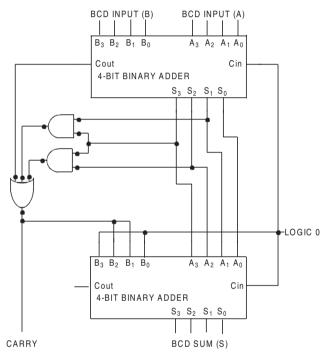

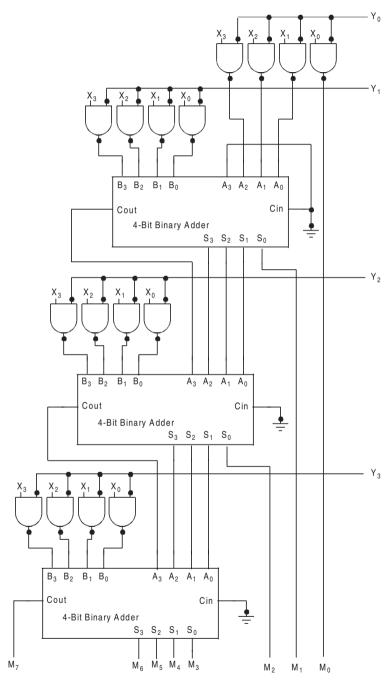

| 5.8    | Combinational Logic with MSI And LSI             | 156         |

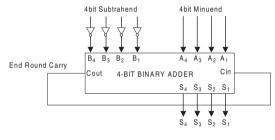

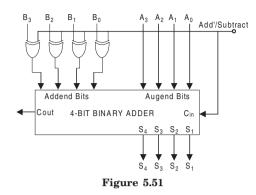

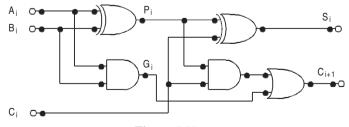

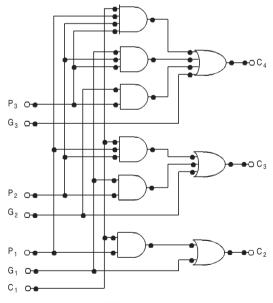

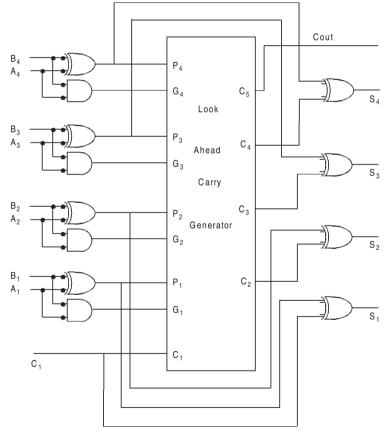

| 5.9    | Four-bit Binary Parallel Adder                   | 157         |

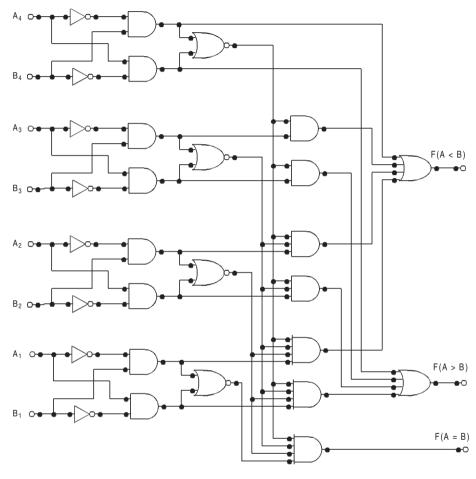

| 5.10   | Magnitude Comparator                             | 167         |

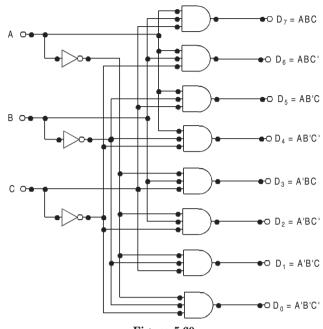

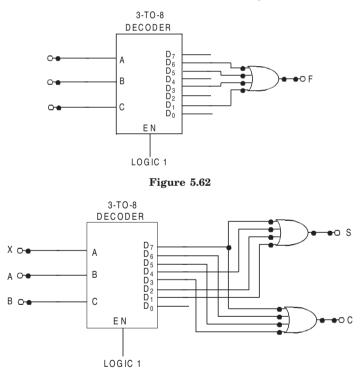

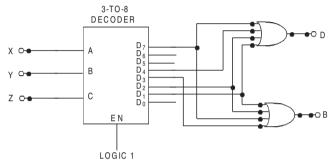

| 5.11   | Decoders                                | 168 |

|--------|-----------------------------------------|-----|

| 5.12   | Encoders                                | 174 |

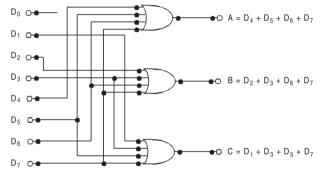

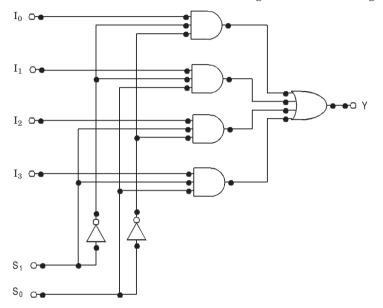

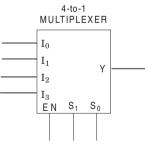

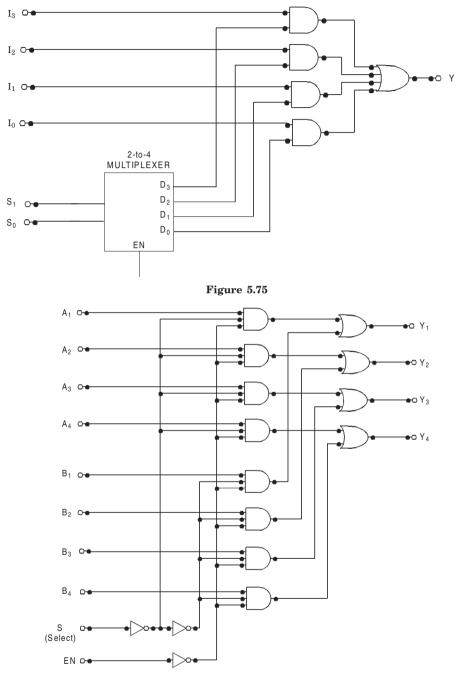

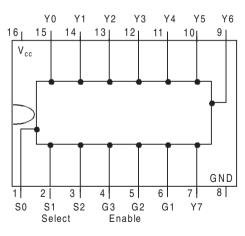

| 5.13   | Multiplexers or Data Selectors          | 175 |

| 5.14   | Demultiplexers or Data Distributors     | 188 |

| 5.15   | Concluding Remarks                      | 190 |

|        | Review Questions                        | 190 |

| 6. PR( | OGRAMMABLE LOGIC DEVICES                | 193 |

| 6.1    | Introduction                            | 193 |

| 6.2    | PLD Notation                            | 195 |

| 6.3    | Read Only Memory (ROM)                  | 195 |

| 6.4    | Programmable Logic Array (PLA)          | 202 |

| 6.5    | Programmable Array Logic (PAL) Devices  | 208 |

| 6.6    | Registered PAL Devices                  | 210 |

| 6.7    | Configurable PAL Devices                | 211 |

| 6.8    | Generic Array Logic Devices             | 211 |

| 6.9    | Field-Programmable Gate Array (FPGA)    | 211 |

| 6.10   | Concluding Remarks                      | 212 |

|        | Review Questions                        | 212 |

| 7. SEG | QUENTIAL LOGIC CIRCUITS                 | 215 |

| 7.1    | Introduction                            | 215 |

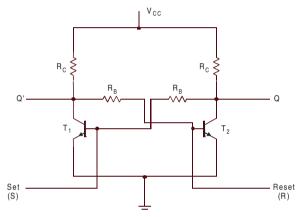

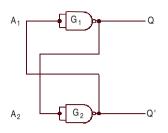

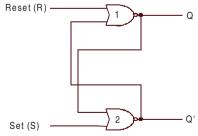

| 7.2    | Flip-flops                              | 216 |

| 7.3    | Types of Flip-flops                     | 218 |

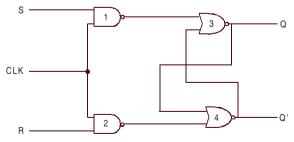

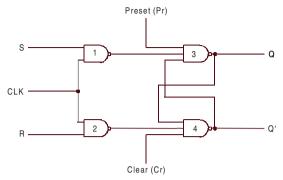

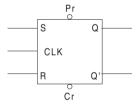

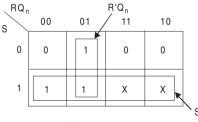

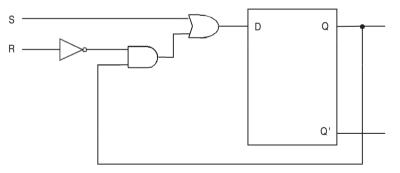

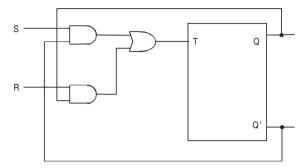

| 7.4    | Clocked S-R Flip-flop                   | 221 |

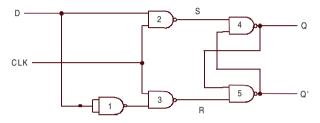

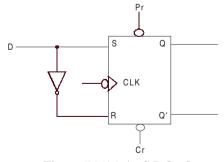

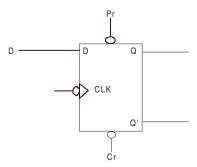

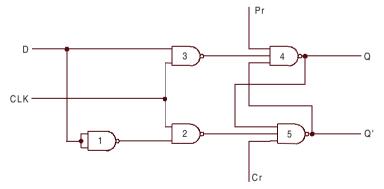

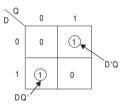

| 7.5    | Clocked D Flip-flop                     | 225 |

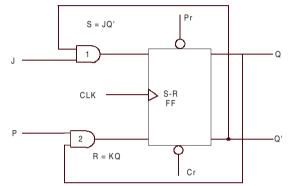

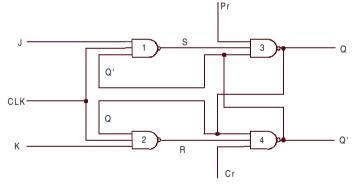

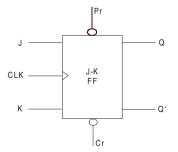

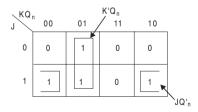

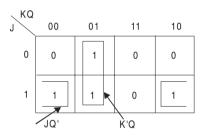

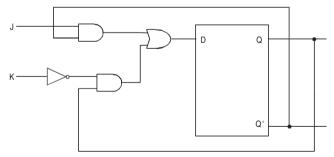

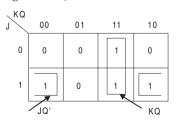

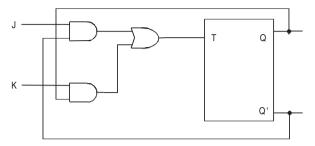

| 7.6    | J-K Flip-flop                           | 228 |

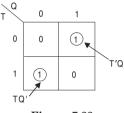

| 7.7    | T Flip-flop                             | 233 |

| 7.8    | Toggling Mode of S-R and D Flip-flops   | 235 |

| 7.9    | Triggering of Flip-flops                | 235 |

| 7.10   | Excitation Table of a Flip-flop         | 237 |

| 7.11   | Interconversion of Flip-flops           | 237 |

| 7.12   | Sequential Circuit Model                | 248 |

| 7.13   | Classification of Sequential Circuits   | 248 |

| 7.14   | Analysis of Sequential Circuits         | 250 |

| 7.15   |                                         |     |

|        | Design Procedure of Sequential Circuits | 254 |

| 8. RE(  | EGISTERS 20                              |     |

|---------|------------------------------------------|-----|

| 8.1     | Introduction                             | 263 |

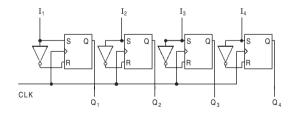

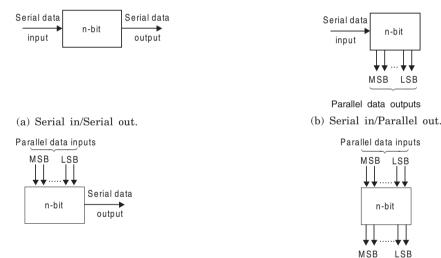

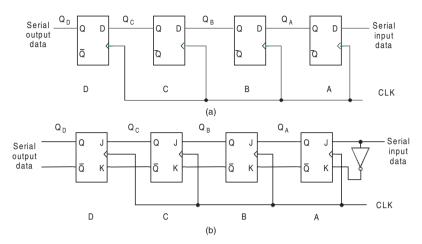

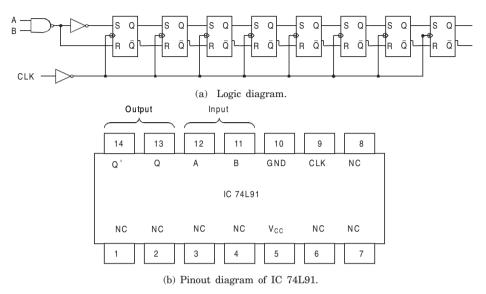

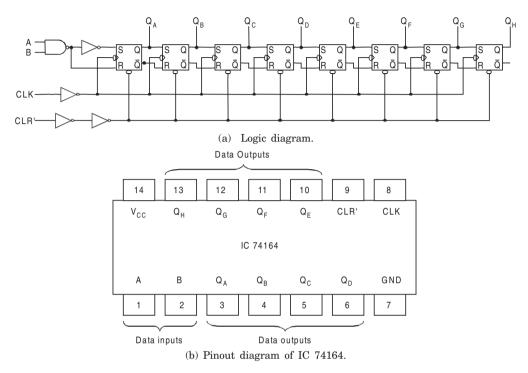

| 8.2     | Shift Register                           | 263 |

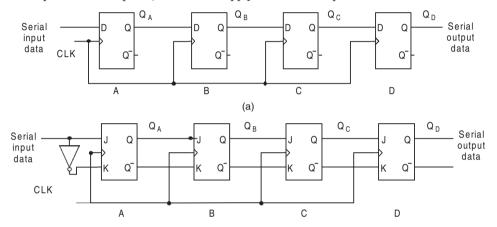

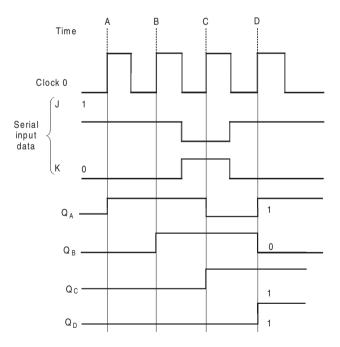

| 8.3     | Serial-in–Serial-out Shift Register      | 264 |

| 8.4     | Serial-in–Parallel-out Register          | 269 |

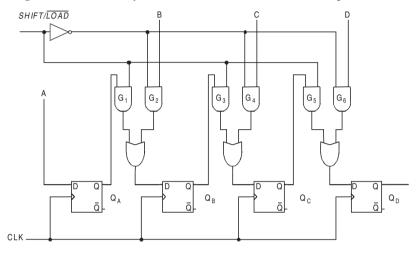

| 8.5     | Parallel-in–Serial-out Register          | 270 |

| 8.6     | Parallel-in–Parallel-out Register        | 272 |

| 8.7     | Universal Register                       | 274 |

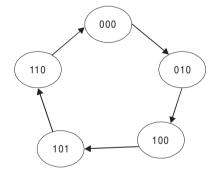

| 8.8     | Shift Register Counters                  | 276 |

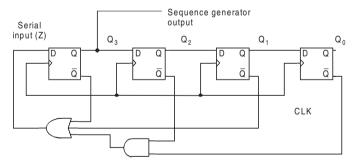

| 8.9     | Sequence Generator                       | 279 |

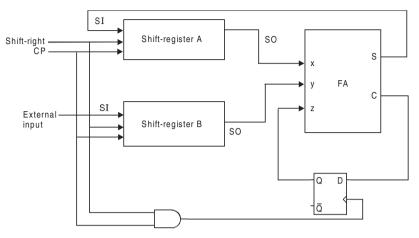

| 8.10    | Serial Addition                          | 283 |

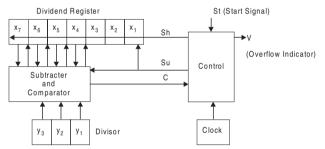

| 8.11    | Binary Divider                           | 284 |

|         | Review Questions                         | 289 |

| 9. CO   | UNTERS                                   | 291 |

| 9.1     | Introduction                             | 291 |

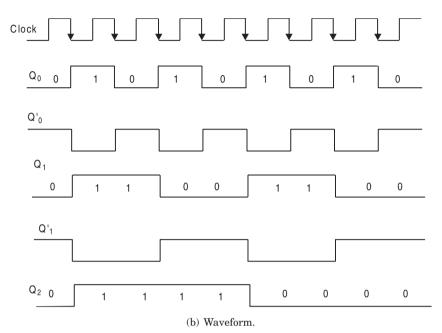

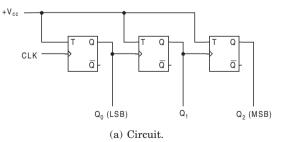

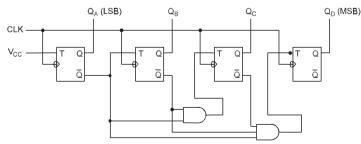

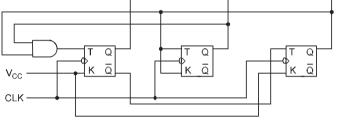

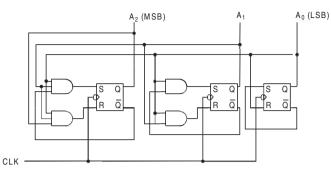

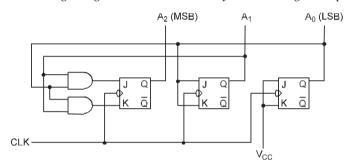

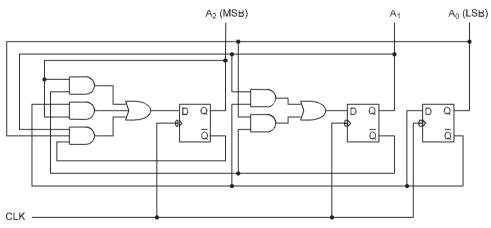

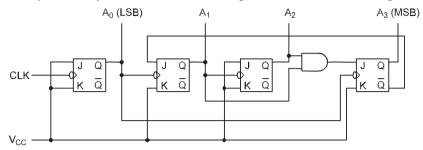

| 9.2     | Asynchronous (Serial or Ripple) Counters | 292 |

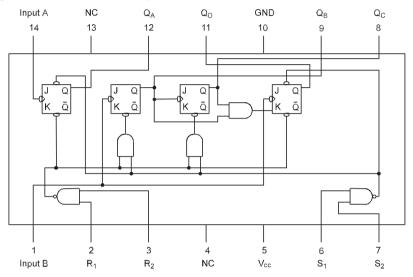

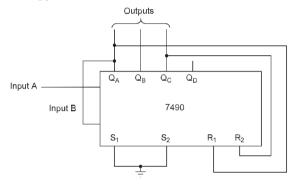

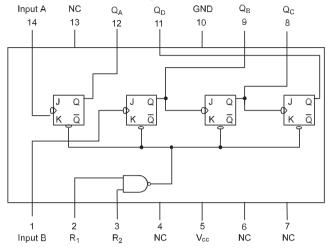

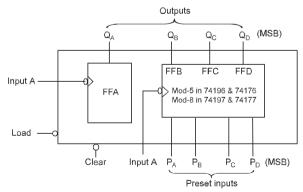

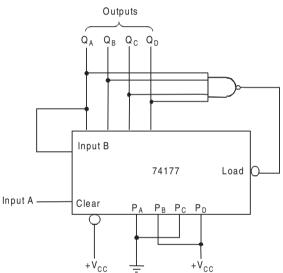

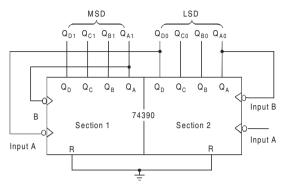

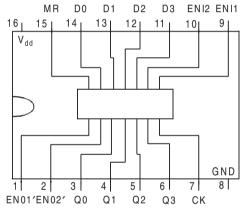

| 9.3     | Asynchronous Counter ICs                 | 302 |

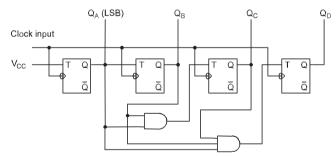

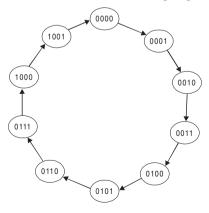

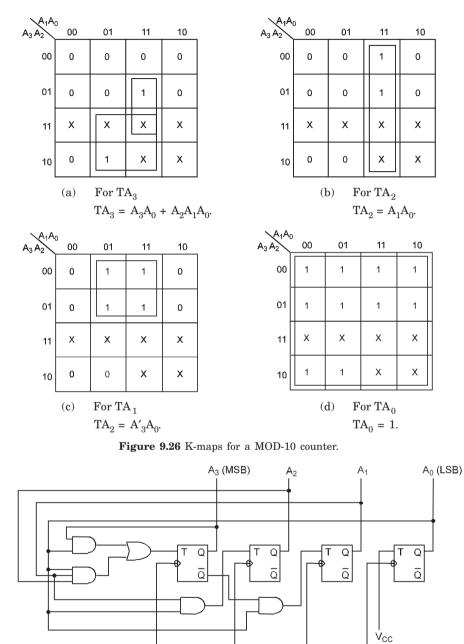

| 9.4     | Synchronous (Parallel) Counters          | 309 |

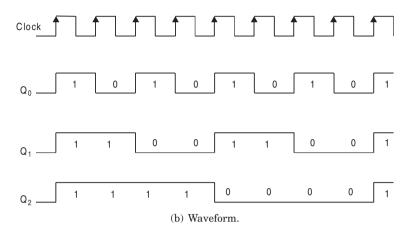

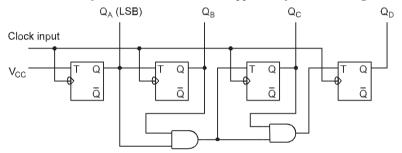

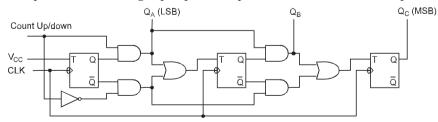

| 9.5     | Synchronous Down-Counter                 | 311 |

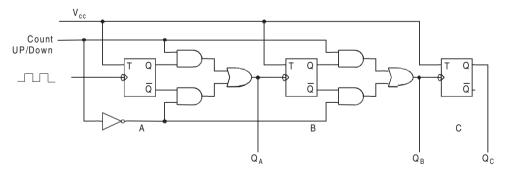

| 9.6     | Synchronous Up-Down Counter              | 312 |

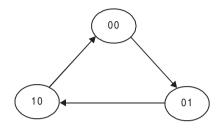

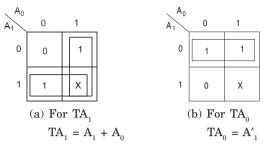

| 9.7     | Design Procedure of Synchronous Counter  | 313 |

| 9.8     | Synchronous/Asynchronous Counter         | 325 |

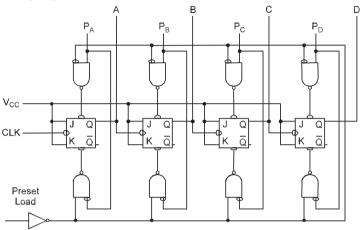

| 9.9     | Presettable Counter                      | 326 |

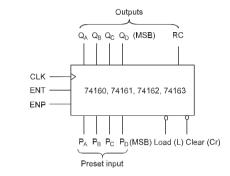

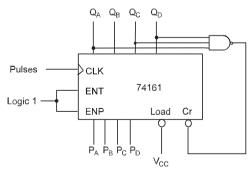

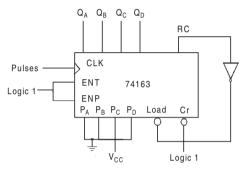

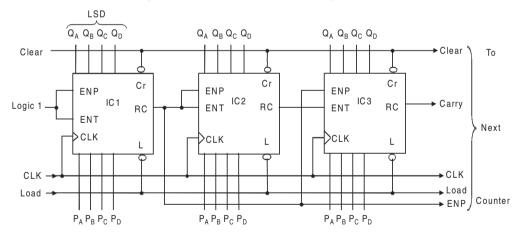

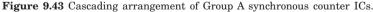

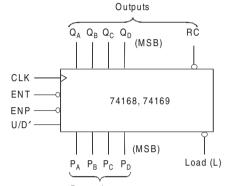

| 9.10    | Synchronous Counter ICs                  | 327 |

| 9.11    | Counter Applications                     | 335 |

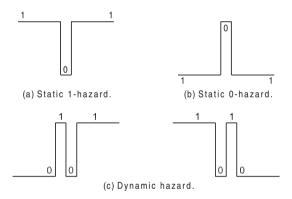

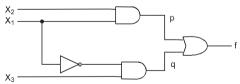

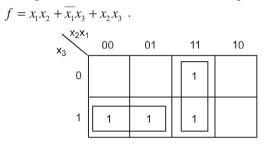

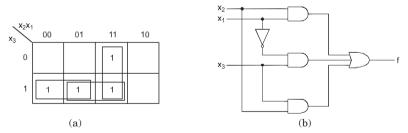

| 9.12    | Hazards in Digital Circuits              | 338 |

|         | Review Questions                         | 344 |

| 10. A/I | D AND D/A CONVERSION                     | 345 |

| 10.1    | Introduction                             | 345 |

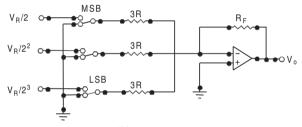

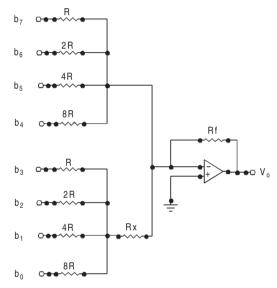

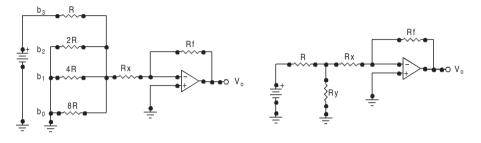

| 10.2    | Digital-to-Analog Converters (DAC)       | 345 |

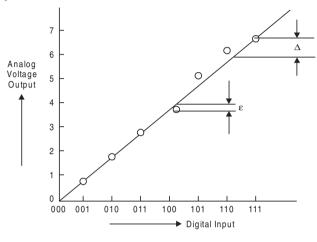

| 10.3    | Specification of D/A Converters          | 355 |

| 10.4    | An Example of a D/A Converter            | 357 |

| 10.5    | Analog-to-Digital Converters             | 360 |

| 10.6    | Specification of an A/D Converter        | 371 |

| 10.7    | An Example of an A/D Converter IC                           | 372 |

|---------|-------------------------------------------------------------|-----|

| 10.8    | Concluding Remarks                                          | 374 |

|         | Review Questions                                            | 374 |

| 11. LO  | GIC FAMILY                                                  | 377 |

| 11.1    | Introduction                                                | 377 |

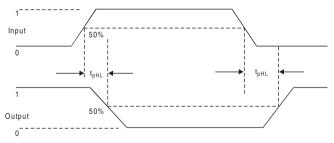

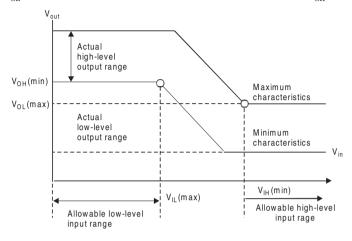

| 11.2    | Characteristics of Digital IC                               | 379 |

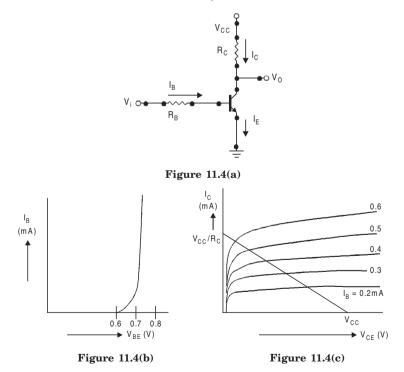

| 11.3    | Bipolar Transistor Characteristics                          | 382 |

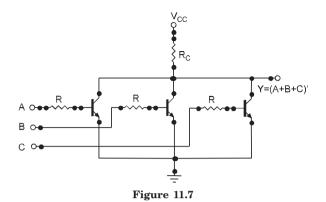

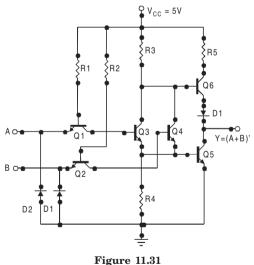

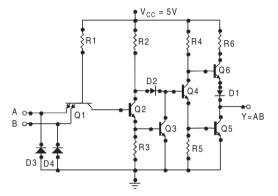

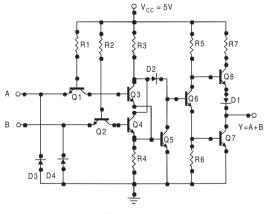

| 11.4    | Resistor-Transistor Logic (RTL)                             | 385 |

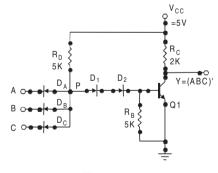

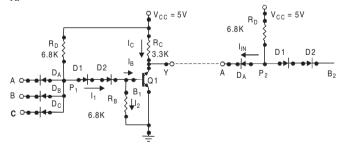

| 11.5    | Diode Transistor Logic (DTL)                                | 387 |

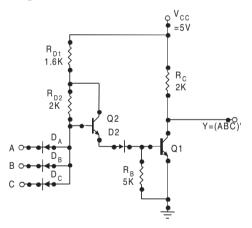

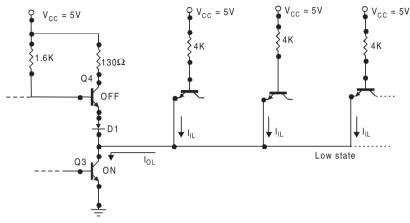

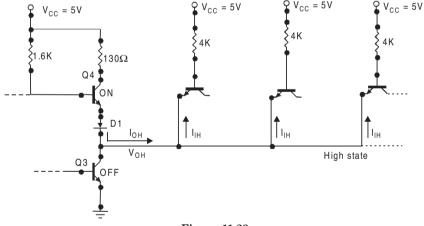

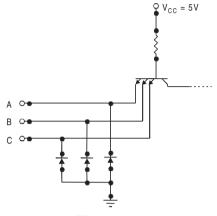

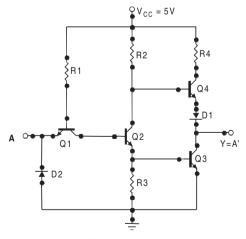

| 11.6    | Transistor Transistor Logic (TTL)                           | 389 |

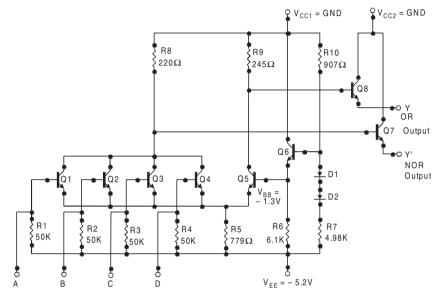

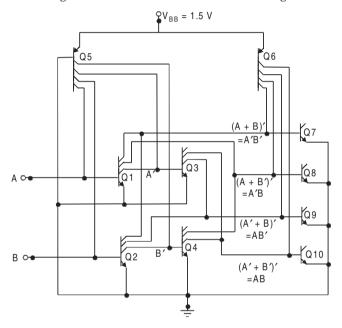

| 11.7    | Emitter-Coupled Logic (ECL)                                 | 407 |

| 11.8    | Integrated-Injection Logic (I <sup>2</sup> L)               | 410 |

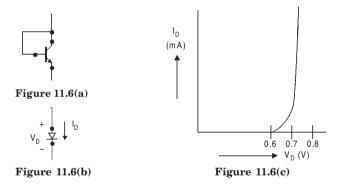

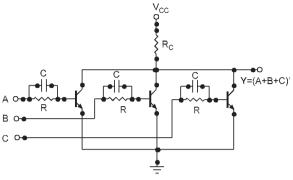

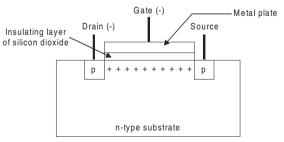

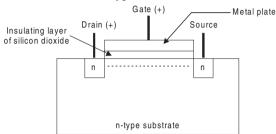

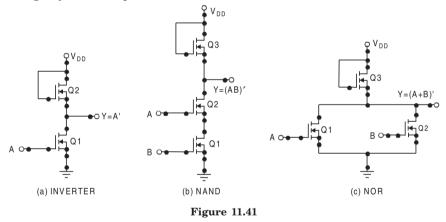

| 11.9    | Metal Oxide Semiconductor (MOS)                             | 412 |

| 11.10   | Comparison of Different Logic Families                      | 420 |

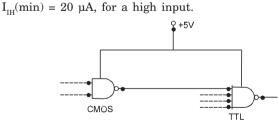

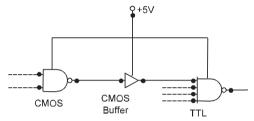

| 11.11   | Interfacing                                                 | 421 |

| 11.12   | Some Examples                                               | 424 |

|         | Review Questions                                            | 427 |

| Append  | lix 1: Alternate Gate Symbols                               | 431 |

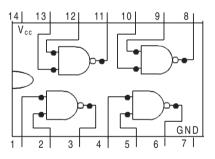

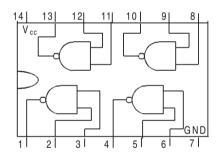

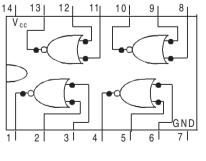

| Append  | lix 2: 74 Series Integrated Circuits                        | 433 |

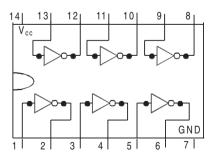

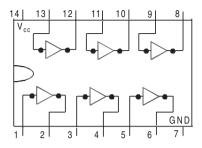

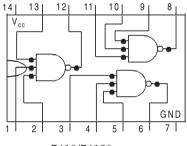

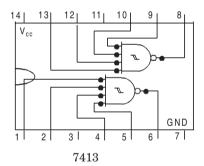

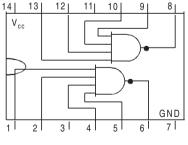

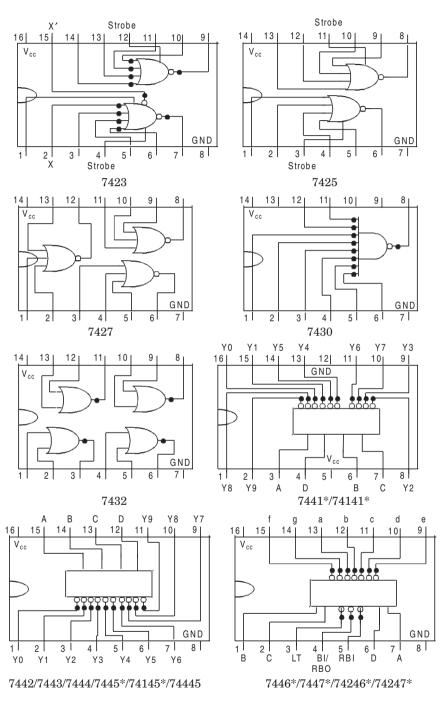

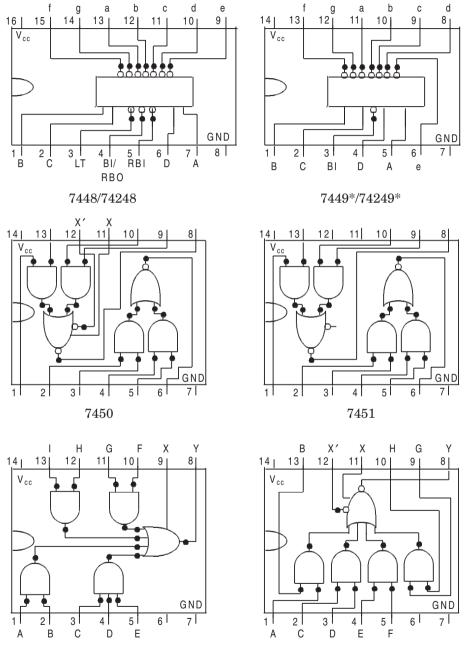

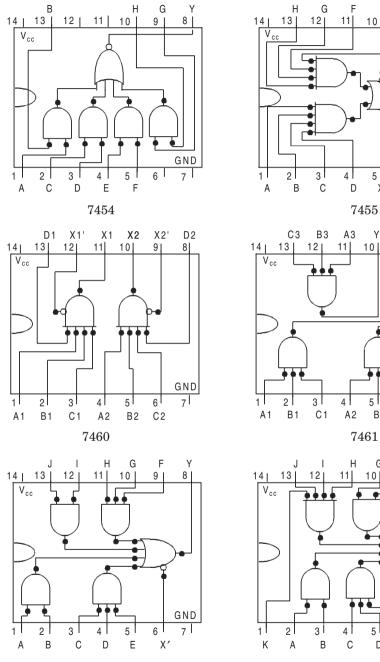

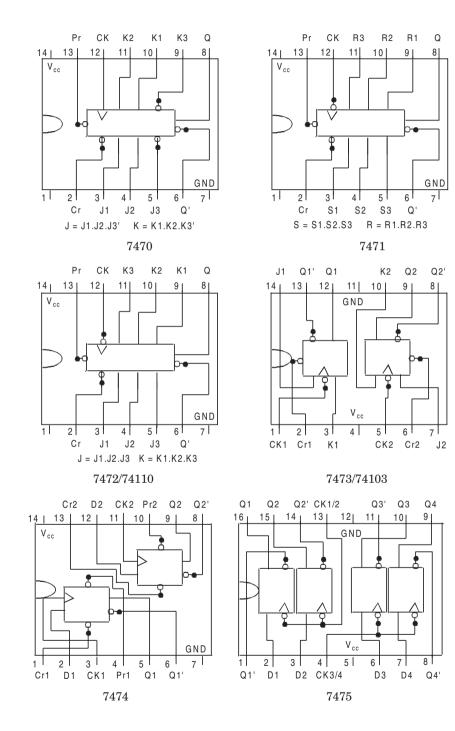

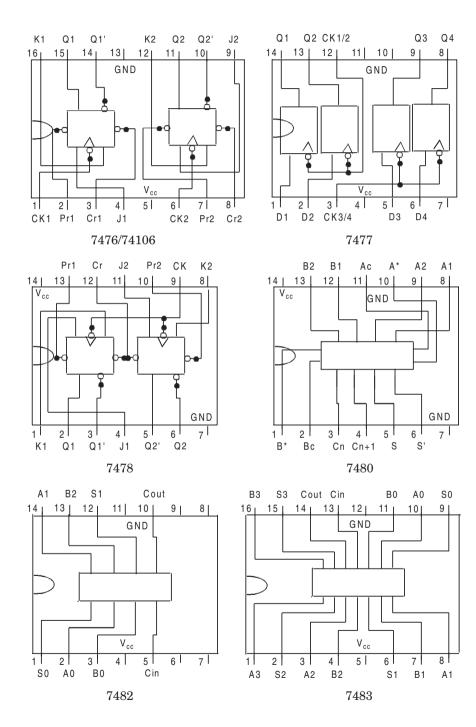

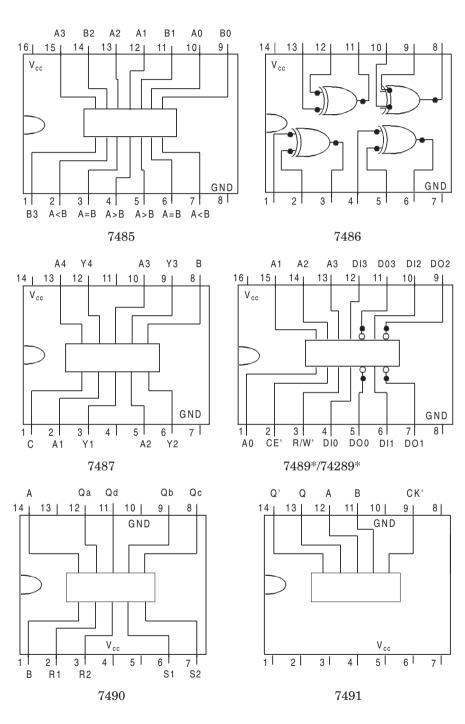

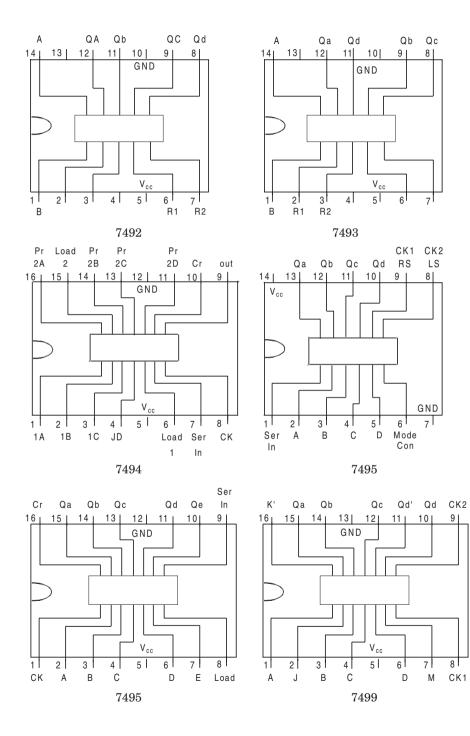

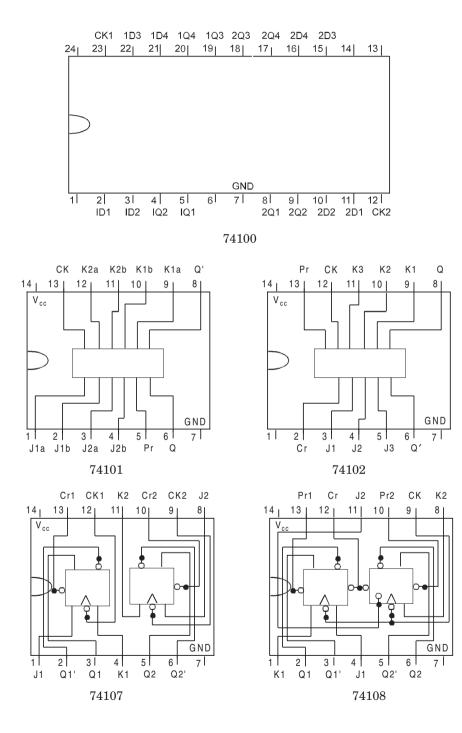

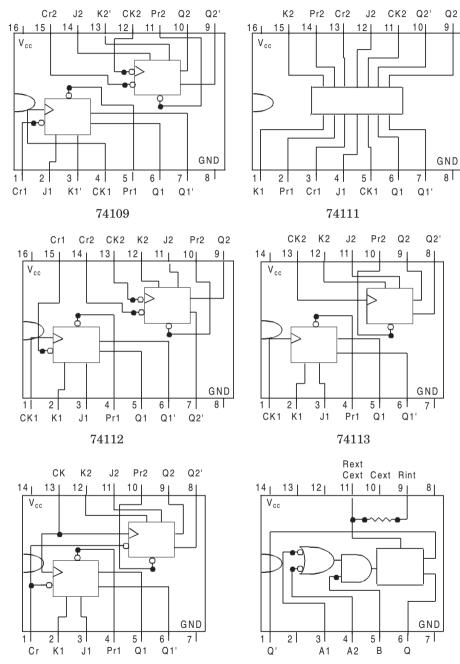

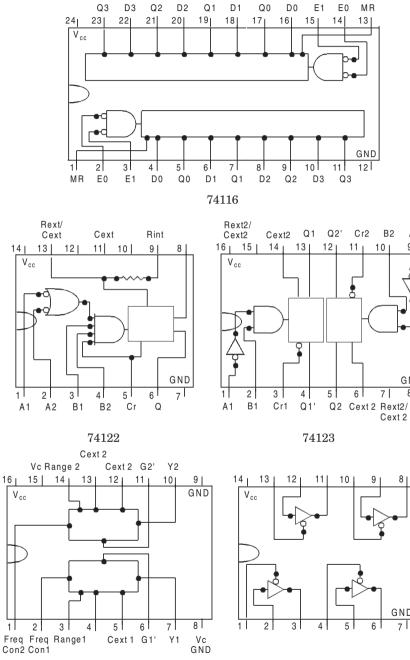

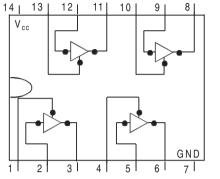

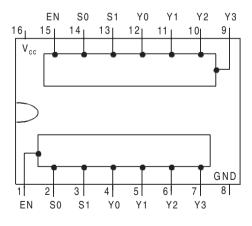

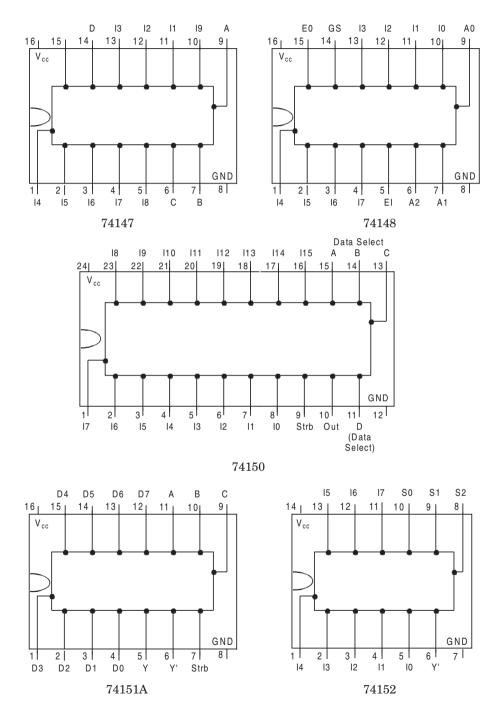

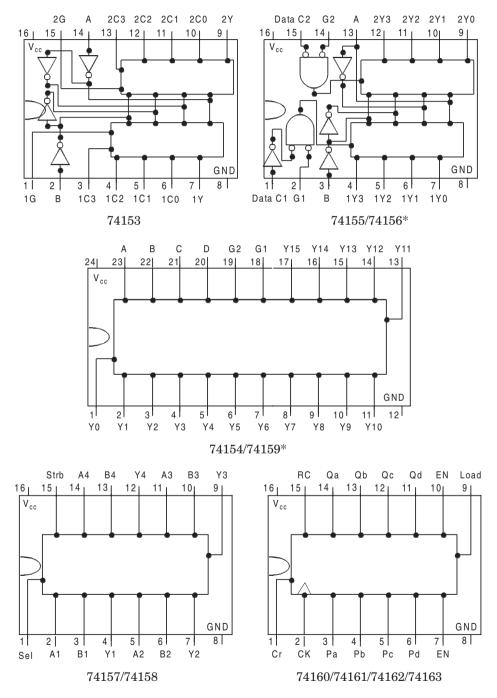

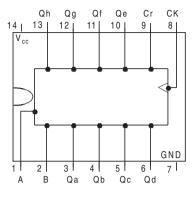

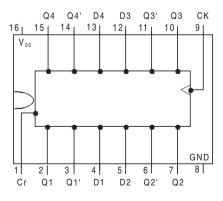

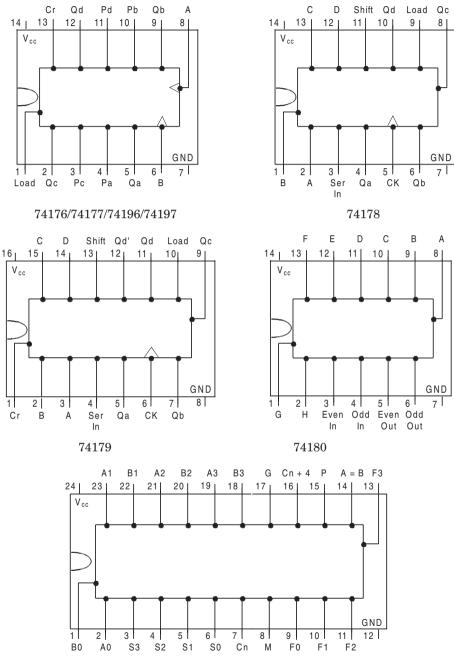

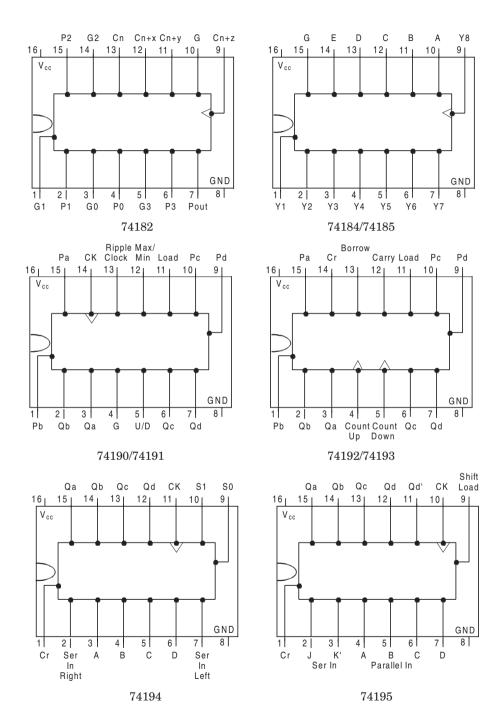

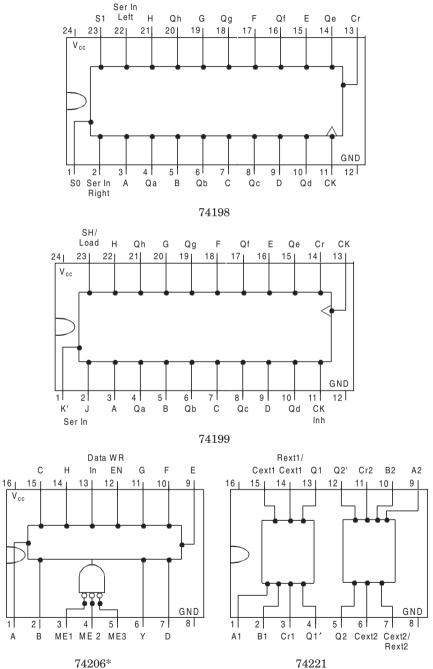

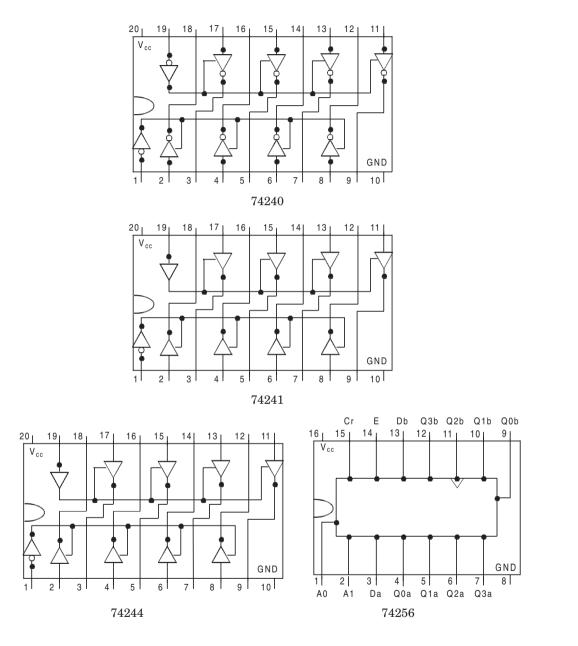

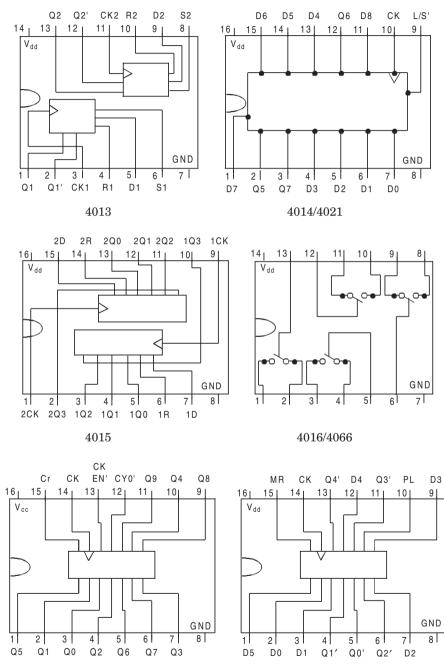

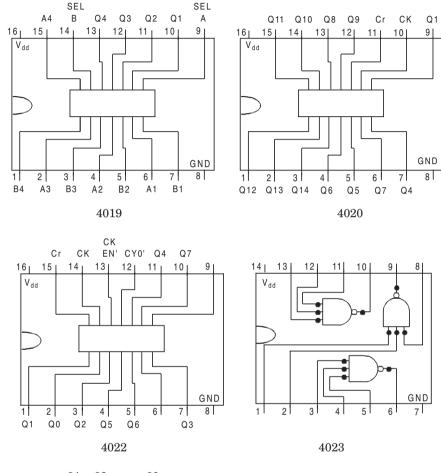

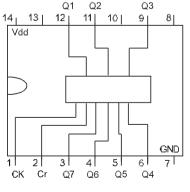

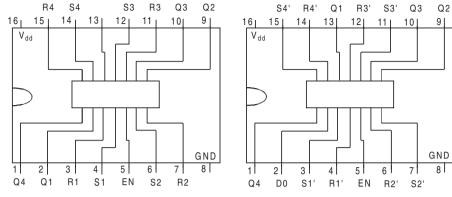

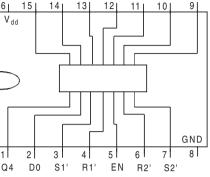

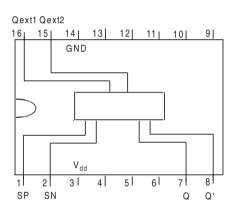

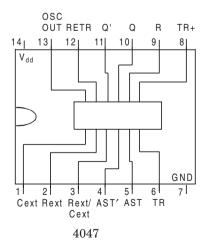

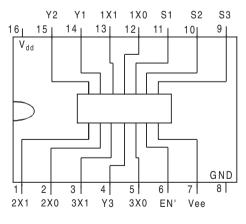

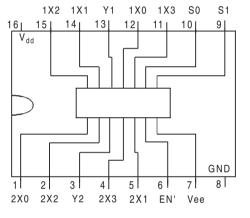

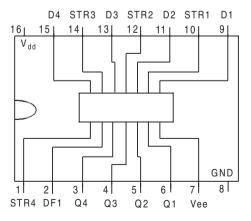

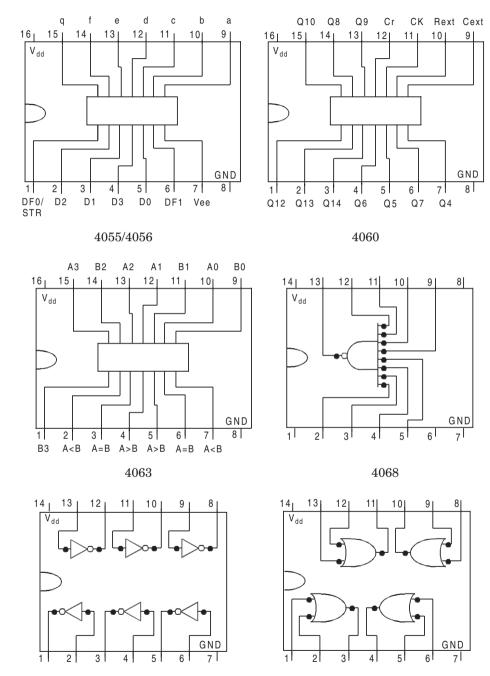

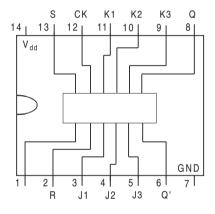

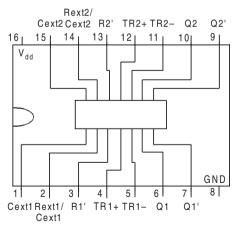

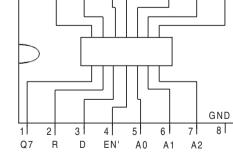

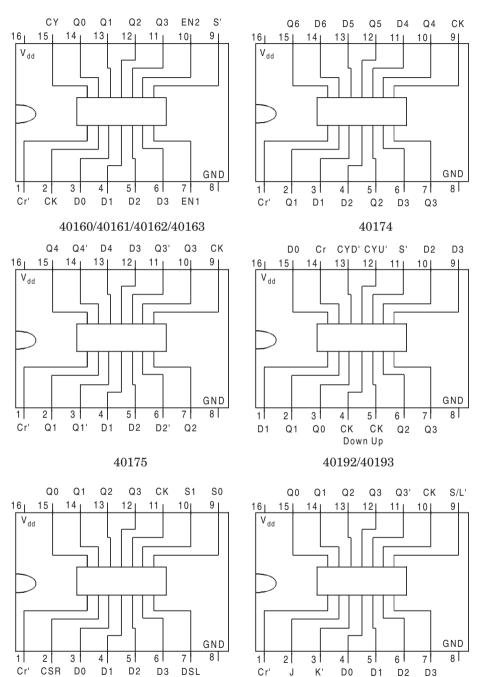

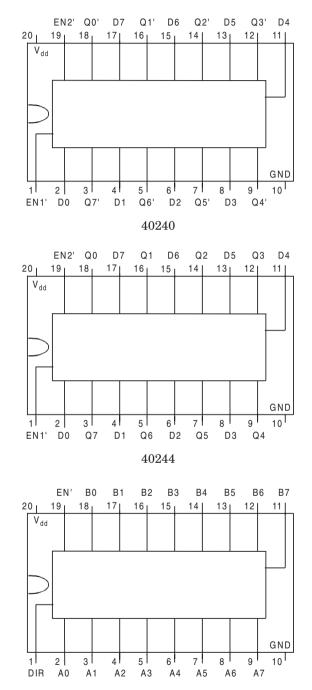

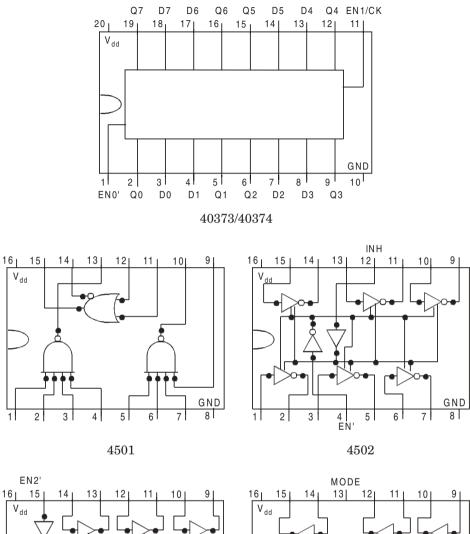

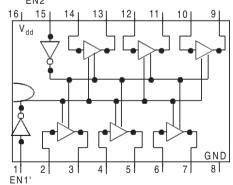

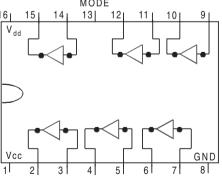

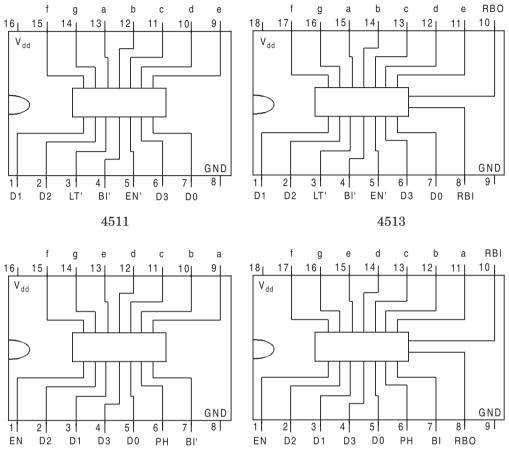

| Append  | lix 3: Pin Configuration of 74 Series Integrated Circuits   | 439 |

| Append  | lix 4: 4000 Series Integrated Circuits                      | 459 |

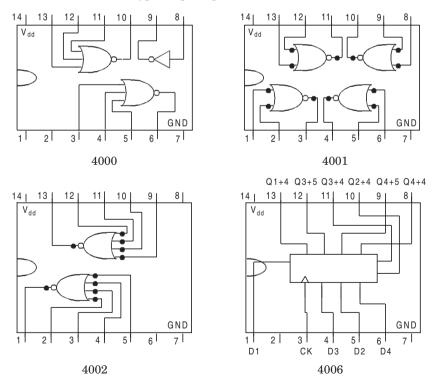

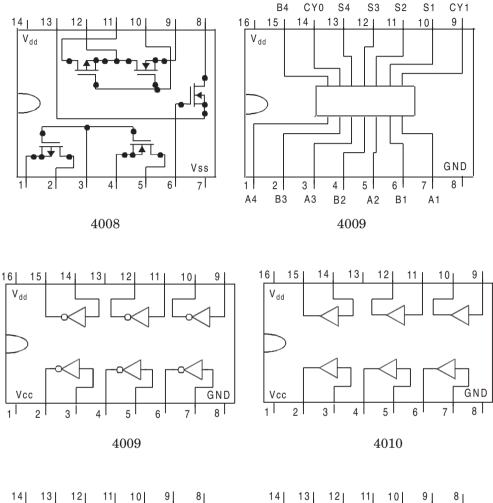

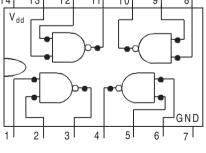

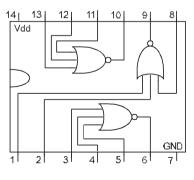

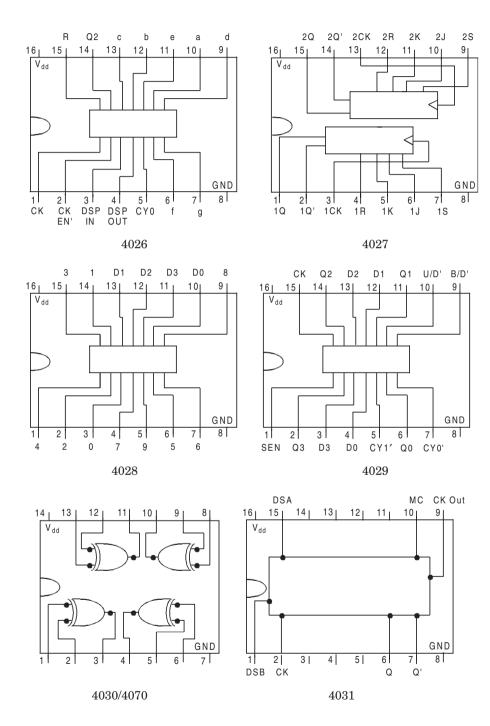

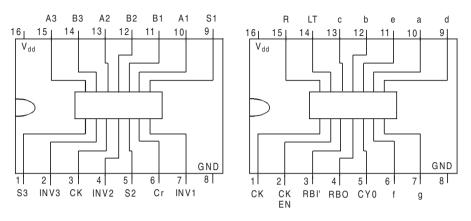

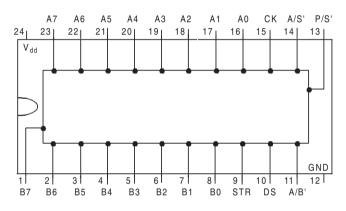

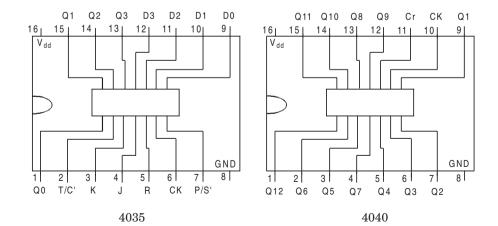

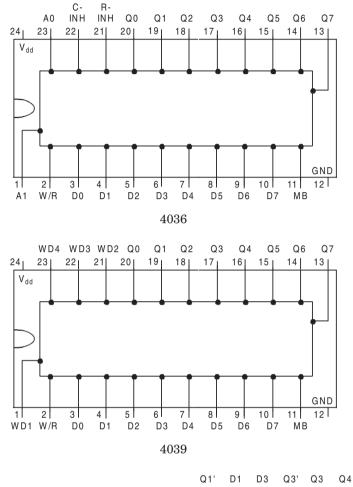

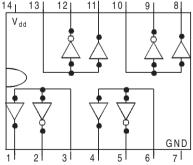

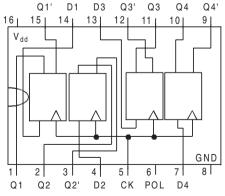

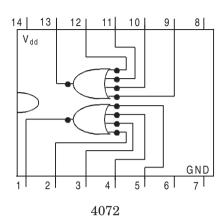

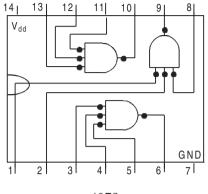

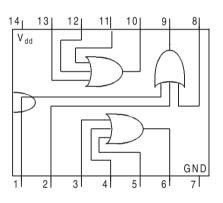

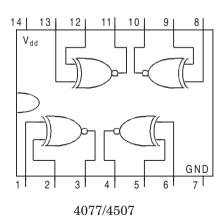

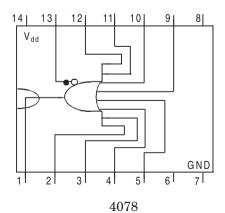

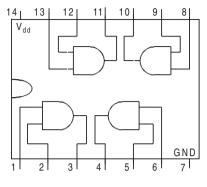

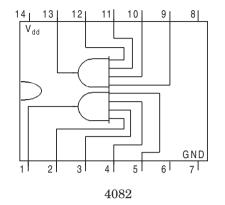

| Append  | lix 5: Pin Configuration of 4000 Series Integrated Circuits | 465 |

| Append  | dix 6: About the CD-ROM                                     | 481 |

| Glossa  | ry                                                          | 483 |

| Bibliog | raphy                                                       | 487 |

| Index   |                                                             | 489 |

## PREFACE

With the advancement of technology, digital logic systems became inevitable and became the integral part of digital circuit design. Digital logic is concerned with the interconnection of digital components and modules, and is a term used to denote the design and analysis of digital systems. Recent technology advancements have led to enhanced usage of digital systems in all disciplines of engineering and have also created the need of in-depth knowledge about digital circuits among the students as well as the instructors. It has been felt that a single textbook dealing with the basic concepts of digital technology with design aspects and applications is the standard requirement. This book is designed to fulfill such a requirement by presenting the basic concepts used in the design and analysis of digital systems, and also providing various methods and techniques suitable for a variety of digital system design applications.

This book is suitable for an introductory course of digital principles with emphasis on logic design as well as for more advanced courses. The contents of this book are chosen and illustrated in such a way that there does not need to be any special background knowledge on the part of the reader.

The philosophy underlying the material presented in this book is to describe the classical methods of design technique. The classical method has been predominant in the past for describing the operation of digital circuits. With the advent of integrated circuits, and especially the introduction of microprocessors, microcontrollers, microcomputers and various LSI components, the classical method seems to be far removed from practical applications. Although the classical method of describing complex digital systems is not directly applicable, the basic concepts of Boolean algebra, combinational logic, and sequential logic procedures are still important for understanding the internal construction of many digital functions. The philosophy of this book is to provide a strong foundation of basic principles through the classical approach before engaging in practical design approach and the use of computer-aided tools. Once the basic concepts are mastered, the utilization of practical design technique and design software become meaningful and allow the students to use them more effectively.

The book is divided into 11 chapters. Each chapter begins with the introduction and ends with review questions and problems. Chapter 1 presents various binary systems suitable for representation of information in digital systems and illustrates binary arithmetic. Chapter 2 describes various codes, conversion, and their utilization in digital systems.

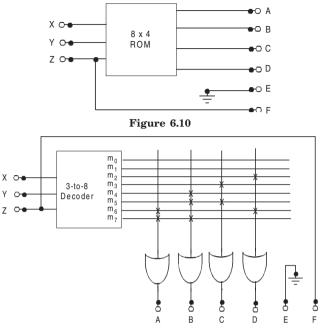

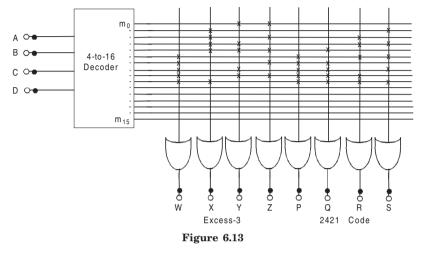

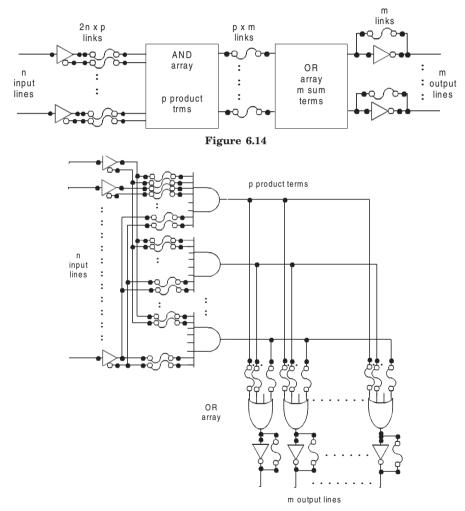

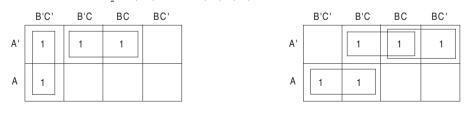

Chapter 3 provides the basic postulates and theorems related to Boolean algebra. The various logic operations and the correlation between the Boolean expression and its implementation with logic gates are illustrated. The various methods of minimization and simplification of Boolean expressions, Karnaugh maps, tabulation method, etc. are explained in Chapter 4. Design and analysis procedures for combinational circuits are provided in Chapter 5. This chapter also deals with the MSI components. Design and implementation of combinational circuits with MSI blocks like adders, decoders, and multiplexers are explained with examples. Chapter 6 introduces LSI components—the read-only memory (ROM) and various programmable logic devices (PLD), and demonstrates design and implementation of complex digital circuits with them.

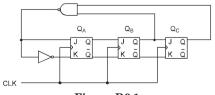

Chapter 7 starts with the introduction of various types of flip-flops and demonstrates the design and implementation of sequential logic networks explaining state table, state diagram, state equations, etc. in detail. Chapter 8 deals with various types of registers and sequence generators. Chapter 9 illustrates synchronous and asynchronous types of counters, and design and application of them in detail.

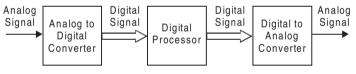

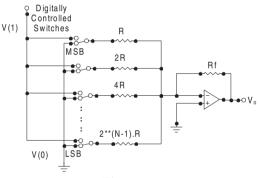

Chapter 10 discusses various methods of digital-to-analog conversion (DAC) as well as analog-to-digital conversion (ADC) techniques. Chapter 11 deals with the various logic families and their characteristics and parameters with respect to propagation delay, noise margin, power dissipation, power requirements, fan out, etc. Appendices have been provided at the end of the book as ready reference for 74-series and 4000-series integrated circuit functions and their pinout configurations.

Clear diagrams and numerous examples have been provided for all the topics, and simple language has been used throughout the book to facilitate understanding of the concepts and to enable the readers to design digital circuits efficiently.

The authors express their thanks to their respective wives and children for their continuous support and enormous patience during the preparation of this book.

The authors welcome any suggestions and corrections for the improvement of the book.

-AUTHORS

Chapter

# Data And Number Systems

#### **1.1 INTRODUCTION**

One of the first things we have to know is that electronics can be broadly classified into two groups, *viz.* analog electronics and digital electronics. Analog electronics deals with things that are continuous in nature and digital electronics deals with things that are discrete in nature. But they are very much interlinked. For example, if we consider a bucket of water, then it is analog in terms of the content *i.e.*, water, but it is discrete in terms of the container, *i.e.*, bucket. Now though in nature most things are analog, still we very often require digital concepts. It is because it has some specific advantages over analog, which we will discuss in due course of time.

Many of us are accustomed with the working of electronic amplifiers. Generally they are used to amplify electronic signals. Now these signals usually have a continuous value and hence can take up any value within a given range, and are known as *analog signals*. The electronic circuits which are used to process such signals are called *analog circuits* and the circuits based on such operation are called analog systems.

On the other side, in a computer, the input is given with the help of the switches. Then this is converted into electronic signals, which have two distinct discrete levels or values. One of them is called HIGH level whereas the other is called LOW level. The signal must always be in either of the two levels. As long as the signal is within a prespecified range of HIGH and LOW, the actual value of the signal is not that important. Such signals are called *digital signals* and the circuit within the device is called a *digital circuit*. The system based on such a concept is an example of a *digital system*.

Since Claude Shannon systemized and adapted the theoretical work of George Boole in 1938, digital techniques saw a tremendous growth. Together with developments in semiconductor technology, and with the progress in digital technology, a revolution in digital electronics happened when the microprocessor was introduced in 1971 by Intel Corporation of America. At present, digital technology has progressed much from the era of vacuum tube circuits to integrated circuits. Digital circuits find applications in computers, telephony, radar navigation, data processing, and many other applications. The general properties of

number systems, methods of their interconversions, and arithmetic operations are discussed in this chapter.

#### 1.2 NUMBER SYSTEMS

There are several number systems which we normally use, such as decimal, binary, octal, hexadecimal, etc. Amongst them we are most familiar with the decimal number system. These systems are classified according to the values of the base of the number system. The number system having the value of the base as 10 is called a decimal number system, whereas that with a base of 2 is called a binary number system. Likewise, the number systems having base 8 and 16 are called octal and hexadecimal number systems respectively.

With a decimal system we have 10 different digits, which are 0, 1, 2, 3, 4, 5, 6, 7, 8, and 9. But a binary system has only 2 different digits—0 and 1. Hence, a binary number cannot have any digit other than 0 or 1. So to deal with a binary number system is quite easier than a decimal system. Now, in a digital world, we can think in binary nature, *e.g.*, a light can be either off or on. There is no state in between these two. So we generally use the binary system when we deal with the digital world. Here comes the utility of a binary system. We can express everything in the world with the help of only two digits *i.e.*, 0 and 1. For example, if we want to express  $25_{10}$  in binary we may write  $11001_2$ . The right most digit in a number system is called the 'Least Significant Bit' (LSB) or 'Least Significant Digit' (LSD). And the left most digit in a number system is called the subscript to make it clear which number system is being used.

In an octal number system there are 8 digits—0, 1, 2, 3, 4, 5, 6, and 7. Hence, any octal number cannot have any digit greater than 7. Similarly, a hexadecimal number system has 16 digits—0 to 9— and the rest of the six digits are specified by letter symbols as A, B, C, D, E, and F. Here A, B, C, D, E, and F represent decimal 10, 11, 12, 13, 14, and 15 respectively. Octal and hexadecimal codes are useful to write assembly level language.

In general, we can express any number in any base or radix "X." Any number with base X, having n digits to the left and m digits to the right of the decimal point, can be expressed as:

$$a_n X^{n-1} + a_{n-1} X^{n-2} + a_{n-2} X^{n-3} + \ldots + a_2 X^1 + a_1 X^0 + b_1 X^{-1} + b_2 X^{-2} + \ldots + b_m X^{-n}$$

where  $a_n$  is the digit in the *n*th position. The coefficient  $a_n$  is termed as the MSD or Most Significant Digit and  $b_m$  is termed as the LSD or the Least Significant Digit.

#### **1.3 CONVERSION BETWEEN NUMBER SYSTEMS**

It is often required to convert a number in a particular number system to any other number system, *e.g.*, it may be required to convert a decimal number to binary or octal or hexadecimal. The reverse is also true, *i.e.*, a binary number may be converted into decimal and so on. The methods of interconversions are now discussed.

#### 1.3.1 Decimal-to-binary Conversion

Now to convert a number in decimal to a number in binary we have to divide the decimal number by 2 repeatedly, until the quotient of zero is obtained. This method of repeated division by 2 is called the 'double-dabble' method. The remainders are noted down for each

#### DATA AND NUMBER SYSTEMS 3

of the division steps. Then the column of the remainder is read in reverse order *i.e.*, from bottom to top order. We try to show the method with an example shown in Example 1.1.

**Example 1.1.** Convert 26<sub>10</sub> into a binary number.

#### Solution.

| Division       | Quotient | Generated remainder |

|----------------|----------|---------------------|

| $\frac{26}{2}$ | 13       | 0                   |

| $\frac{13}{2}$ | 6        | 1                   |

| $\frac{6}{2}$  | 3        | 0                   |

| $\frac{3}{2}$  | 1        | 1                   |

| $\frac{1}{2}$  | 0        | 1                   |

Hence the converted binary number is 11010<sub>2</sub>.

#### 1.3.2 Decimal-to-octal Conversion

Similarly, to convert a number in decimal to a number in octal we have to divide the decimal number by 8 repeatedly, until the quotient of zero is obtained. This method of repeated division by 8 is called 'octal-dabble.' The remainders are noted down for each of the division steps. Then the column of the remainder is read from bottom to top order, just as in the case of the double-dabble method. We try to illustrate the method with an example shown in Example 1.2.

**Example 1.2.** Convert 426<sub>10</sub> into an octal number.

Solution.

| Division        | Quotient | Generated remainder |

|-----------------|----------|---------------------|

| $\frac{426}{8}$ | 53       | 2                   |

| $\frac{53}{8}$  | 6        | 5                   |

| $\frac{6}{8}$   | 0        | 6                   |

Hence the converted octal number is  $652_8$ .

#### 1.3.3 Decimal-to-hexadecimal Conversion

The same steps are repeated to convert a number in decimal to a number in hexadecimal. Only here we have to divide the decimal number by 16 repeatedly, until the quotient of zero is obtained. This method of repeated division by 16 is called 'hex-dabble.' The remainders are noted down for each of the division steps. Then the column of the remainder is read from bottom to top order as in the two previous cases. We try to discuss the method with an example shown in Example 1.3.

# **Example 1.3.** Convert $348_{10}$ into a hexadecimal number. Solution.

| Division         | Quotient | Generated remainder |

|------------------|----------|---------------------|

| $\frac{348}{16}$ | 21       | 12                  |

| $\frac{21}{16}$  | 1        | 5                   |

| $\frac{1}{16}$   | 0        | 1                   |

Hence the converted hexadecimal number is  $15C_{16}$ .

#### 1.3.4 Binary-to-decimal Conversion

Now we discuss the reverse method, *i.e.*, the method of conversion of binary, octal, or hexadecimal numbers to decimal numbers. Now we have to keep in mind that each of the binary, octal, or hexadecimal number system is a positional number system, *i.e.*, each of the digits in the number systems discussed above has a positional weight as in the case of the decimal system. We illustrate the process with the help of examples.

**Example 1.4.** Convert 10110, into a decimal number.

| Solution. | The binary number given is | $1 \ 0 \ 1 \ 1 \ 0$ |

|-----------|----------------------------|---------------------|

|           | Positional weights         | $4\ 3\ 2\ 1\ 0$     |

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$1 \times 2^{4} + 0 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0}$$

= 16 + 0 + 4 + 2 + 0

= 22<sub>10</sub>.

Hence we find that here, for the sake of conversion, we have to multiply each bit with its positional weights depending on the base of the number system.

#### 1.3.5 Octal-to-decimal Conversion

**Example 1.5.** Convert 3462<sub>8</sub> into a decimal number.

| Solution. | The octal number given is | 3462 |

|-----------|---------------------------|------|

|           | Positional weights        | 3210 |

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$3 \times 8^{3} + 4 \times 8^{2} + 6 \times 8^{1} + 2 \times 8^{0}$$

= 1536 + 256 + 48 + 2

= 1842<sub>10</sub>.

#### 1.3.6 Hexadecimal-to-decimal Conversion

Example 1.6. Convert 42AD<sub>16</sub> into a decimal number.

Solution.

The hexadecimal number given is

Positional weights

3 2 1 0

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$$4 \times 16^{3} + 2 \times 16^{2} + 10 \times 16^{1} + 13 \times 16^{0}$$

= 16384 + 512 + 160 + 13

= 17069<sub>10</sub>.

#### 1.3.7 Fractional Conversion

Example 1.8

So far we have dealt with the conversion of integer numbers only. Now if the number contains the fractional part we have to deal in a different way when converting the number from a different number system (*i.e.*, binary, octal, or hexadecimal) to a decimal number system or vice versa. We illustrate this with examples.

Example 1.7. Convert 1010.011, into a decimal number.

| Solution. | The binary number given is | 1010.011       |

|-----------|----------------------------|----------------|

|           | Positional weights         | 3 2 1 0 -1-2-3 |

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

| $1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} + 1 \times 2^{-3}$ |

|-------------------------------------------------------------------------------------------------------------------|

| = 8 + 0 + 2 + 0 + 0 + 0.25 + 0.125                                                                                |

| $= 10.375_{10}$ .                                                                                                 |

| 3. Convert 362.35, into a decimal number.                                                                         |

Solution. The octal number given is 3 6 2. 3 5

Positional weights 2 1 0 -1-2

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

> $3 \times 8^{2} + 6 \times 8^{1} + 2 \times 8^{0} + 3 \times 8^{-1} + 5 \times 8^{-2}$ = 192 + 48 + 2 + 0.375 + 0.078125 = 242.453125<sub>10</sub>.

**Example 1.9.** Convert 42A.12<sub>16</sub> into a decimal number.

Solution. The hexadecimal number given is 4 2 A. 1 2

| Positional weights | 2 1 0 -1-2 |

|--------------------|------------|

|--------------------|------------|

The positional weights for each of the digits are written in italics below each digit. Hence the decimal equivalent number is given as:

$\begin{array}{l} 4 \times 16^2 + 2 \times 16^1 + 10 \times 16^0 + 1 \times 16^{-1} + 1 \times 16^{-2} \\ = & 1024 + 32 + 10 + 0.0625 + 0.00390625 \\ = & 1066.06640625_{10}. \end{array}$

| Solution. Divi                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $25_{10}$ into a binar<br>Quotient                                                                                                                                | Generated remainder                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                | $\frac{25}{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                                                                                                                | 1                                                                                                                                   |

| -                                                                                                              | $\frac{2}{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                 | 0                                                                                                                                   |

| -                                                                                                              | $\frac{6}{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                 | 0                                                                                                                                   |

| _                                                                                                              | $\frac{6}{2}$ $\frac{3}{2}$ $\frac{1}{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                 | 1                                                                                                                                   |

| -                                                                                                              | $\frac{1}{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                 | 1                                                                                                                                   |

| Therefore,                                                                                                     | (25) <sub>10</sub> =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | = (11001) <sub>2</sub>                                                                                                                                            |                                                                                                                                     |

| Fractional Part                                                                                                | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                   |                                                                                                                                     |

|                                                                                                                | 0.625                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.250                                                                                                                                                             | ★ 0.500                                                                                                                             |

|                                                                                                                | <u></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u></u> /                                                                                                                                                         | <u></u>                                                                                                                             |

|                                                                                                                | 1.250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.500                                                                                                                                                             | 1.000                                                                                                                               |

|                                                                                                                | ¥                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ¥                                                                                                                                                                 | ¥                                                                                                                                   |

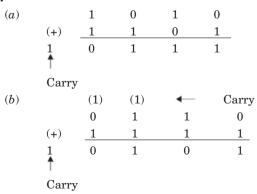

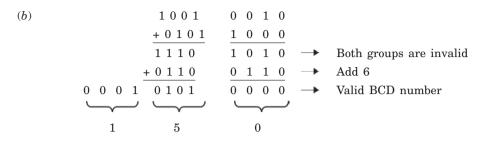

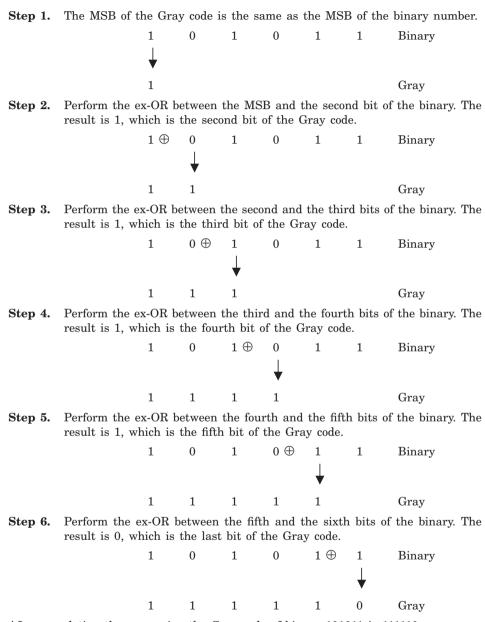

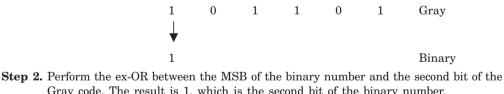

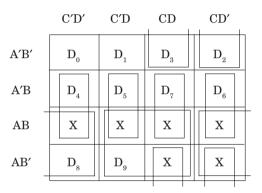

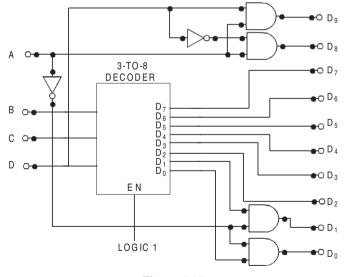

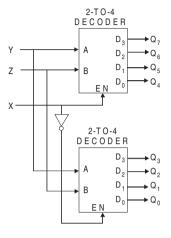

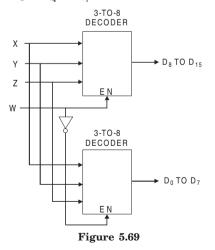

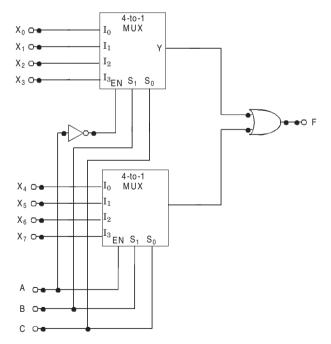

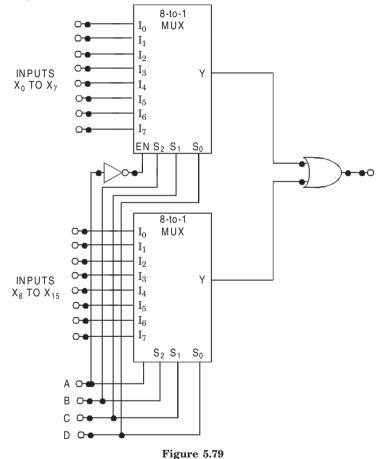

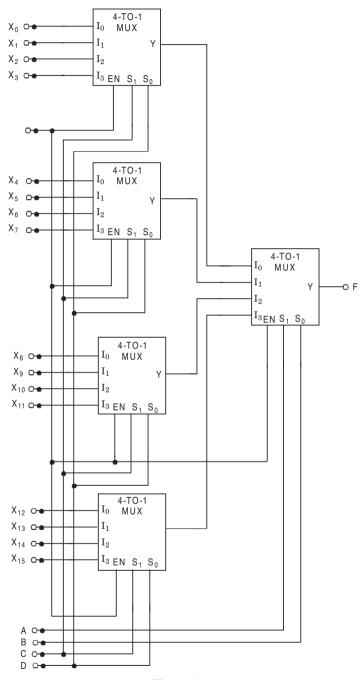

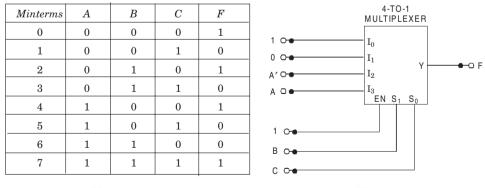

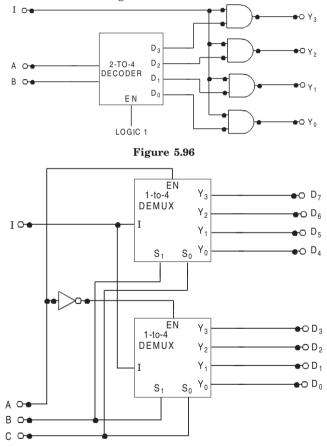

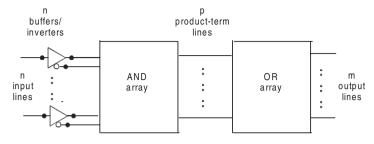

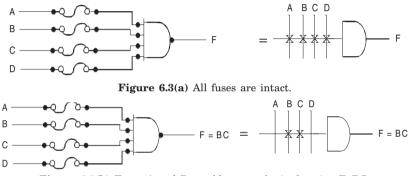

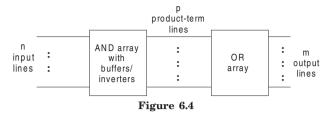

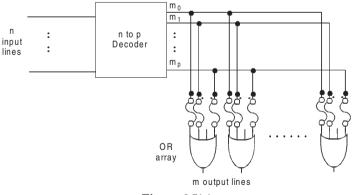

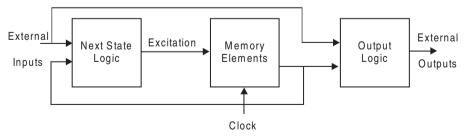

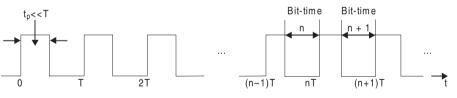

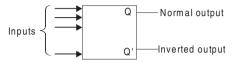

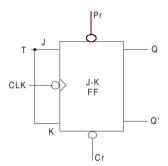

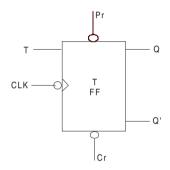

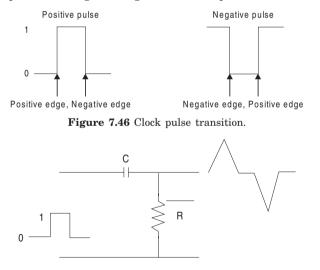

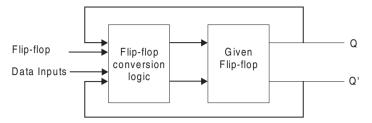

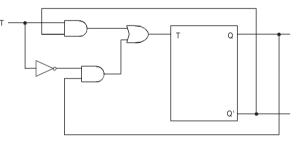

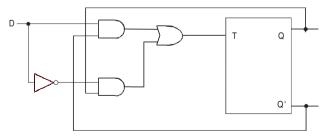

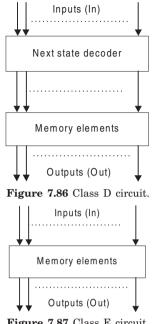

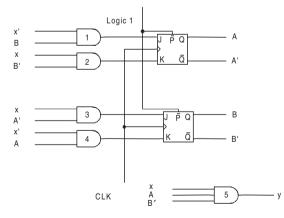

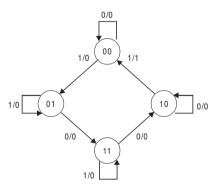

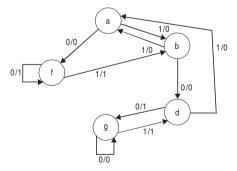

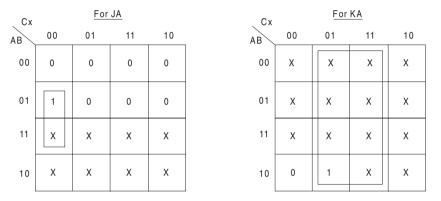

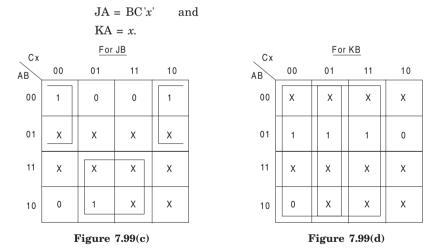

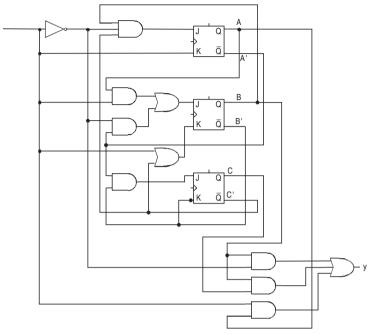

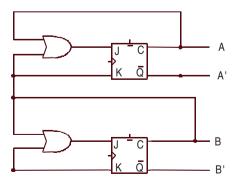

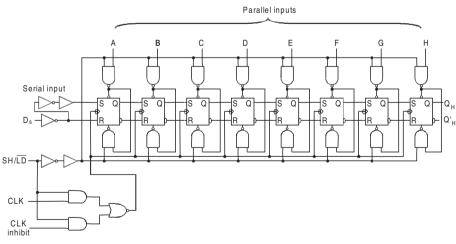

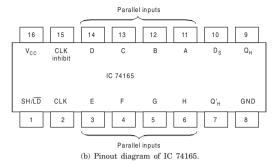

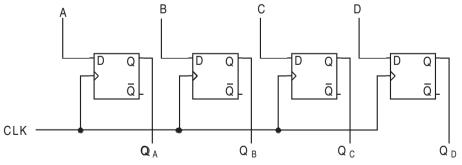

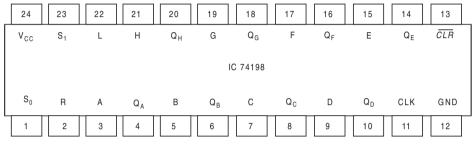

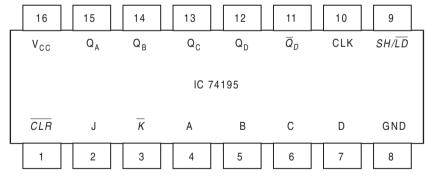

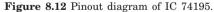

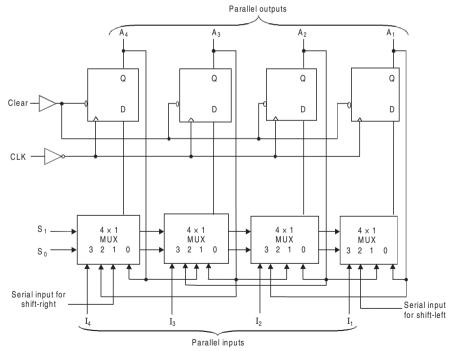

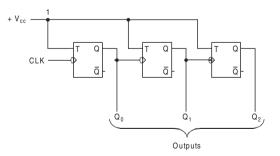

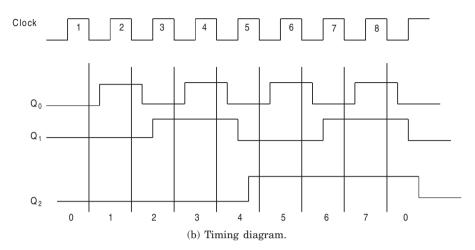

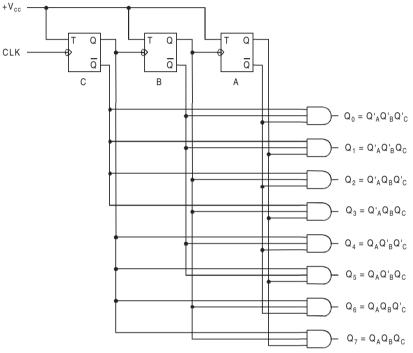

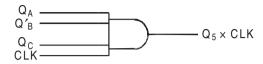

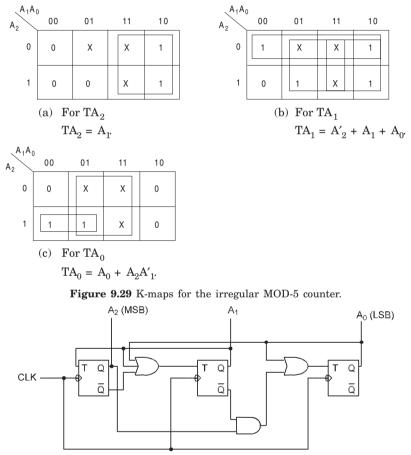

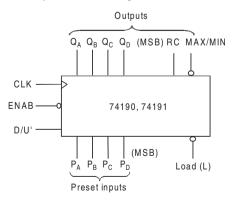

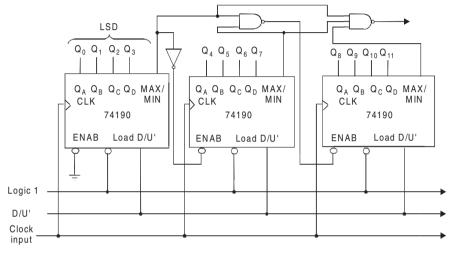

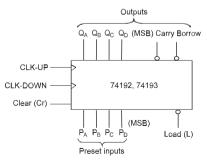

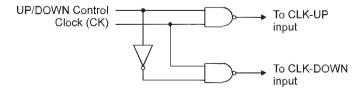

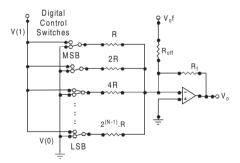

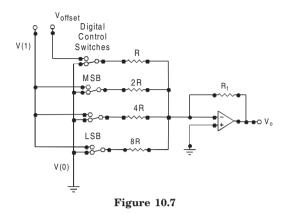

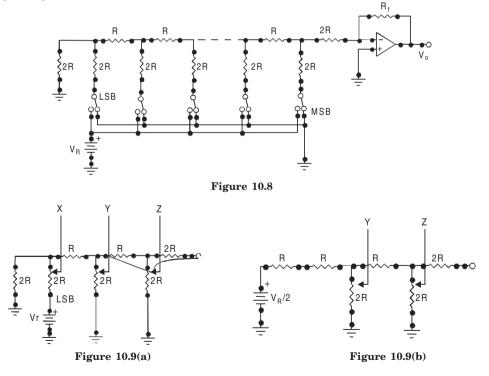

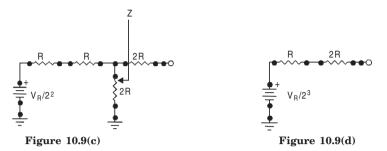

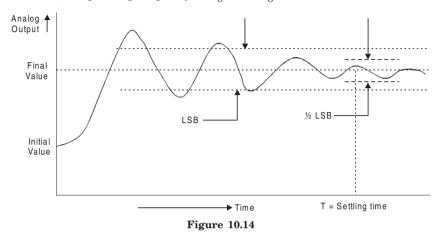

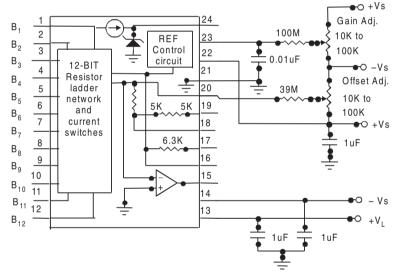

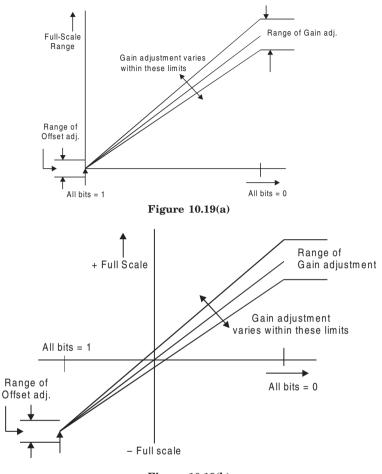

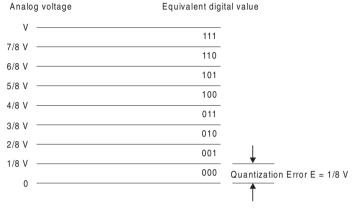

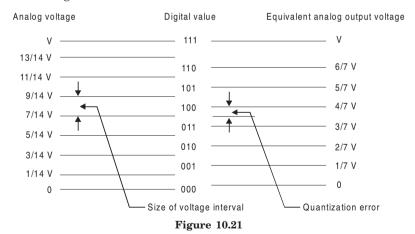

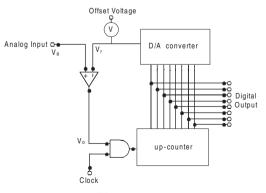

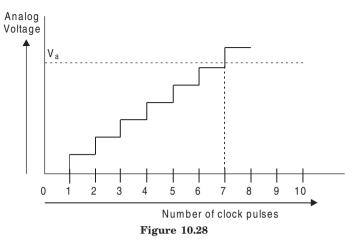

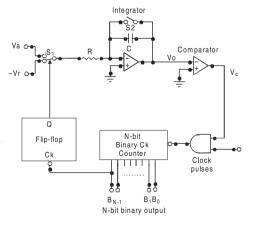

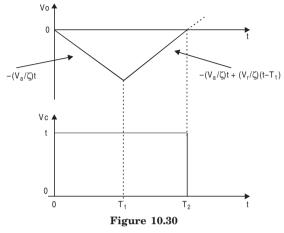

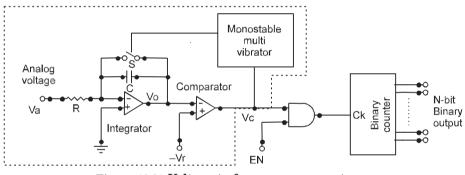

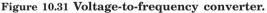

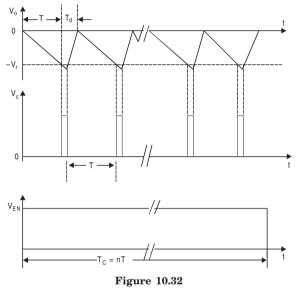

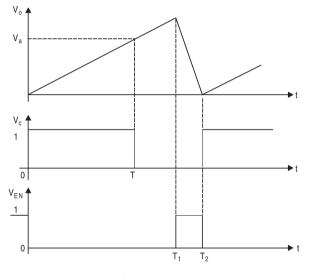

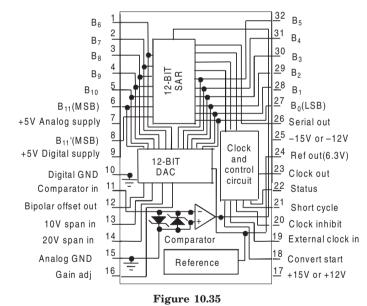

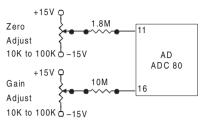

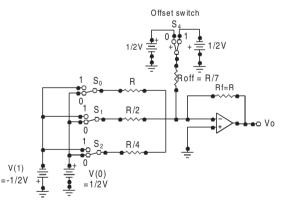

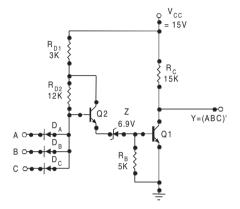

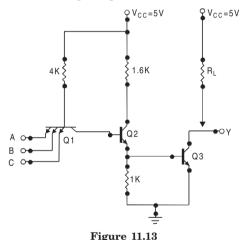

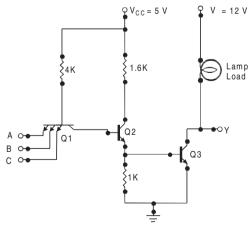

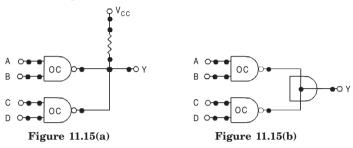

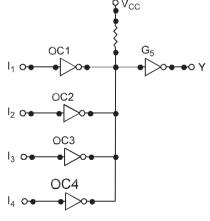

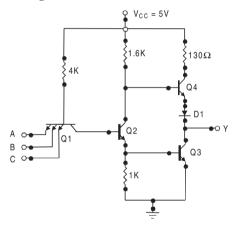

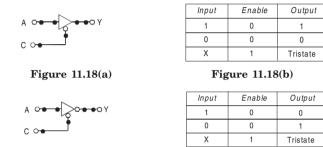

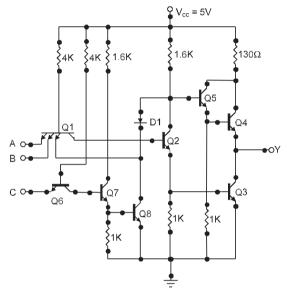

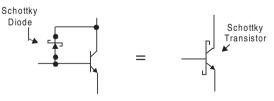

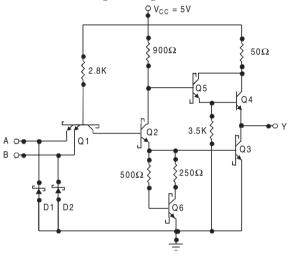

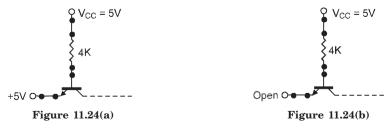

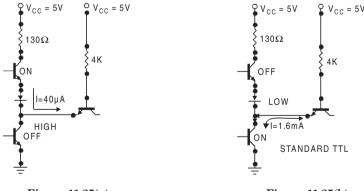

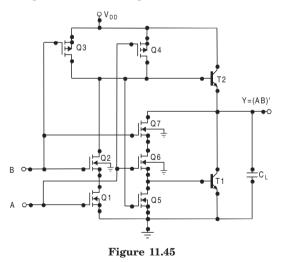

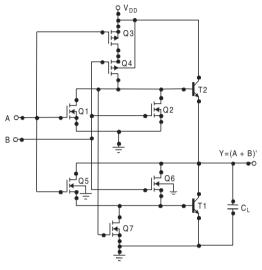

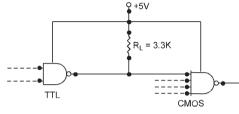

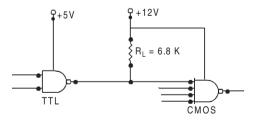

|                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                                                 | 1                                                                                                                                   |